# [Instruction]

# **Contents**

| Cha | pte  | r 1: PLC Ladder Diagram and the Coding Rules of Mnemonic                        | ;    |

|-----|------|---------------------------------------------------------------------------------|------|

| 1   | .1   | The Operation Principle of Ladder Diagram······                                 | 1-1  |

|     | 1.1. | 1 Combination Logic 1                                                           | 1-1  |

|     | 1.1. | 2 Sequential Logic ······ 1                                                     | 1-2  |

| 1   | .2   | Differences Between Conventional and PLC Ladder Diagram ······················· | 1-3  |

| 1   | .3   | Ladder Diagram Structure and Terminology ·······                                | 1-5  |

| 1   | .4   | The Coding Rules of Mnemonic 1                                                  | 1-8  |

| 1   | .5   | The De-Composition of a Network                                                 | 1-11 |

| 1   | .6   | Using Temporary Relays······                                                    | 1-12 |

| 1   | .7   | Program Simplification Techniques                                               | 1-13 |

| Cha | pte  | r 2: FBS-PLC Memory Allocation                                                  |      |

| 2   | .1   | FBs-PLC Memory Allocation2                                                      | 2-1  |

| 2   | .2   | Digital and Register Allocations2                                               | 2-2  |

| 2   | .3   | Special Relay Details2                                                          | 2-3  |

| 2   | .4   | Special Registers Details ·······2                                              | 2-7  |

| Cha | pte  | r 3: FBS-PLC Instruction Lists                                                  |      |

| 3   | .1   | Sequential Instructions ······                                                  | 3-1  |

| 3   | .2   | Function Instructions ······                                                    | 3-2  |

| Cha | •    | r 4: Sequential Instructions                                                    |      |

| 4   |      | Valid Operand of Sequential Instructions                                        |      |

| 4   | .2   | Element Description ······                                                      |      |

|     | 4.2. |                                                                                 |      |

|     | 4.2. |                                                                                 |      |

|     | 4.2. | ·                                                                               |      |

|     | 4.2. | ·                                                                               |      |

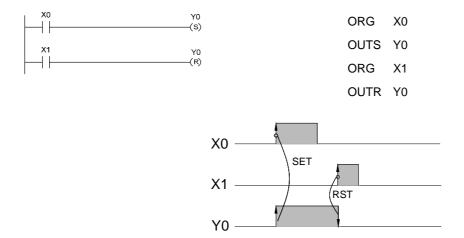

|     | 4.2. | 5 Set Coil and Reset Coil                                                       | 1-5  |

|     | _    | Node Operation Instructions                                                     | . –  |

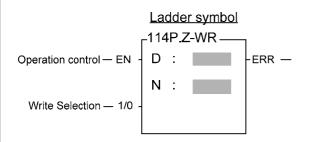

## Chapter 5: Description of Function Instructions

| 5.1   | The Format of Function Instructions       |                       | 5-1  |

|-------|-------------------------------------------|-----------------------|------|

| 5.    | 1.1 Input Control                         |                       | 5-1  |

| 5.    | 1.2 Instruction Number and Derivative Ins | structions            | 5-2  |

| 5.    | 1.3 Operand                               |                       | 5-3  |

| 5.    | 1.4 Functions Output (FO)                 |                       | 5-6  |

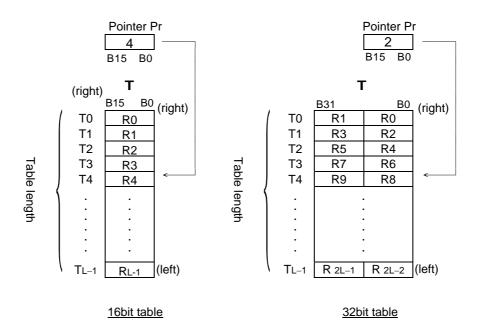

| 5.2   | Use Index Register(XR) for Indirect A     | ddressing             | 5-6  |

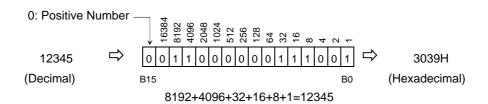

| 5.3   | Numbering System                          |                       | 5-9  |

| 5.    | 3.1 Binary Code and Related Terminologi   | es                    | 5-9  |

| 5.    | 3.2 The Coding of Numeric Numbers for I   | FBs-PLC               | 5-10 |

| 5.    | 3.3 Range of Numeric Value                |                       | 5-10 |

| 5.    | 3.4 Representation of Numeric Value       |                       | 5-10 |

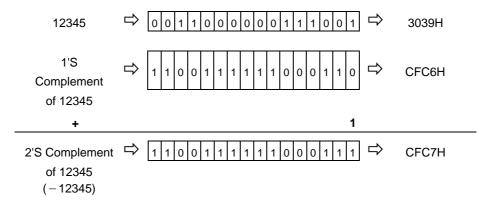

| 5.    | 3.5 Representation of Negative Number .   |                       | 5-11 |

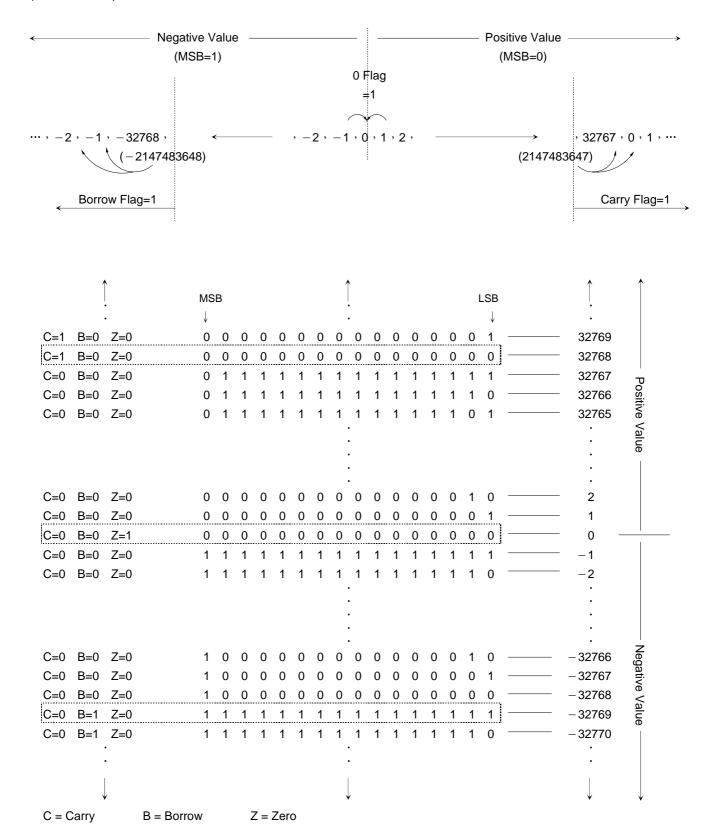

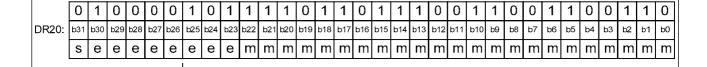

| 5.    | 3.6 Representation of Floating Point Num  | ber                   | 5-11 |

| 5.4   | Overflow and Underflow of Increment       | (+1) or Decrement(-1) | 5-12 |

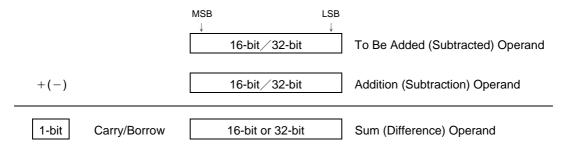

| 5.5   |                                           | tion                  |      |

|       | ,                                         |                       |      |

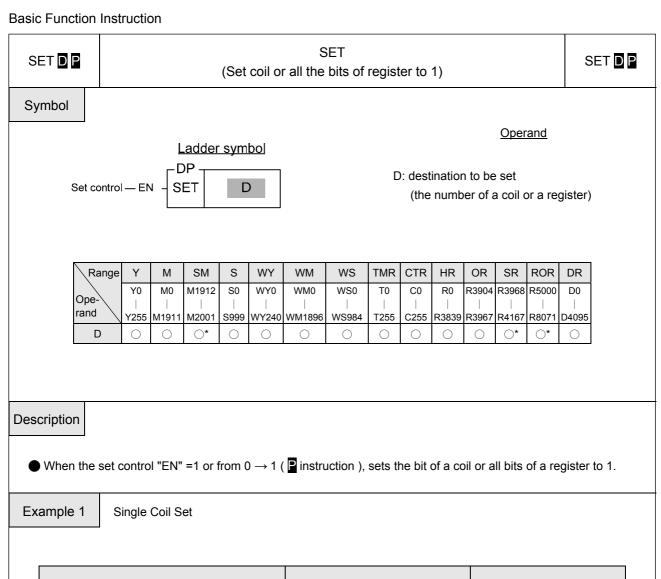

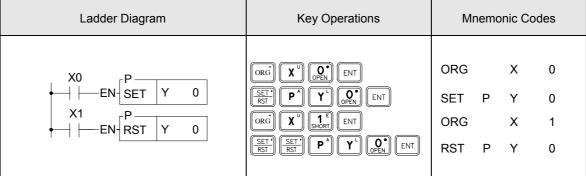

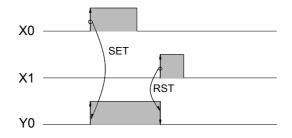

| Chapt | ter 6: Basic Function Instructi           | ons                   |      |

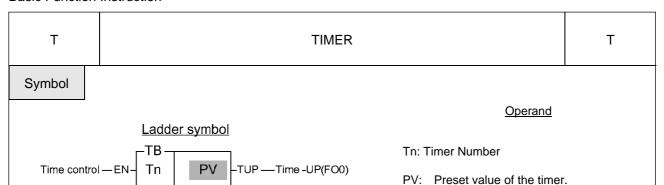

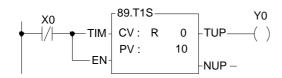

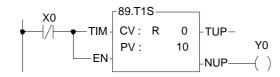

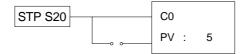

| •     | Т                                         | (Timer)               | 6-2  |

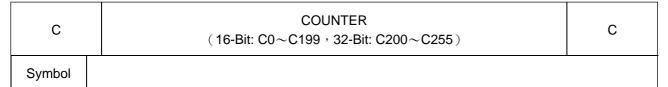

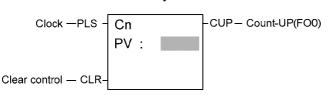

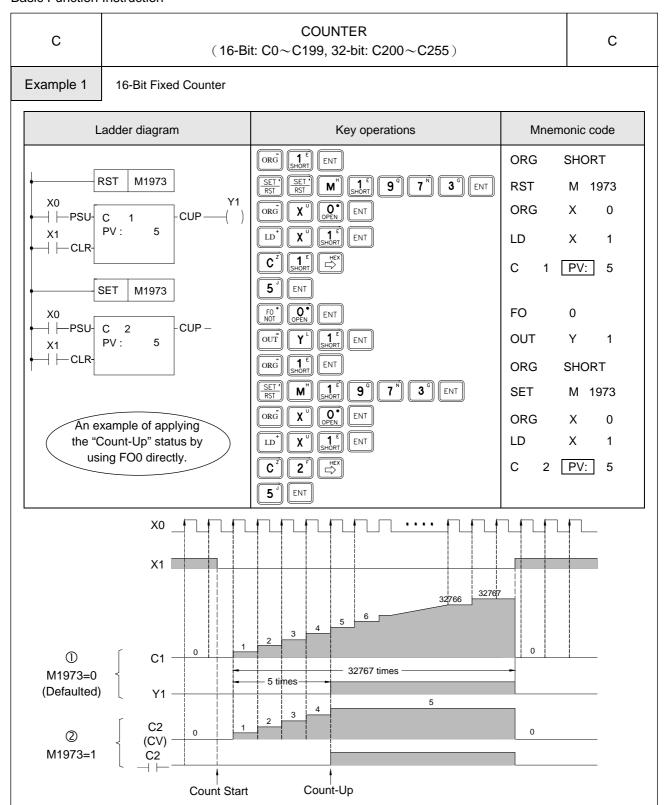

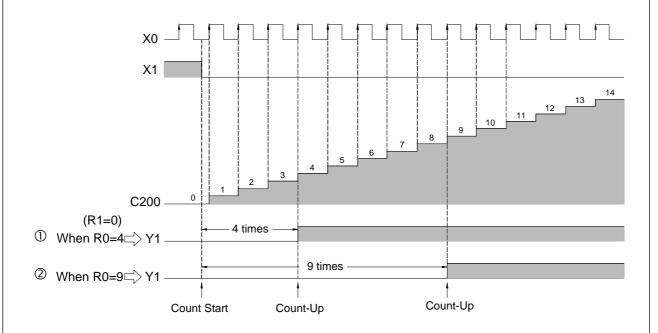

| •     | С                                         | (Counter)             | 6-5  |

| •     | Set                                       | (SET)                 | 6-8  |

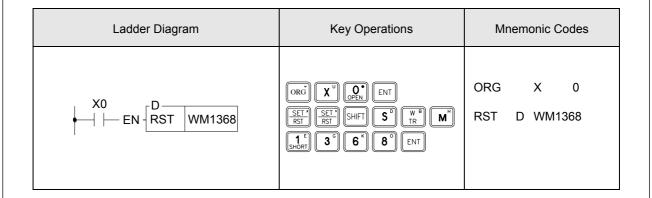

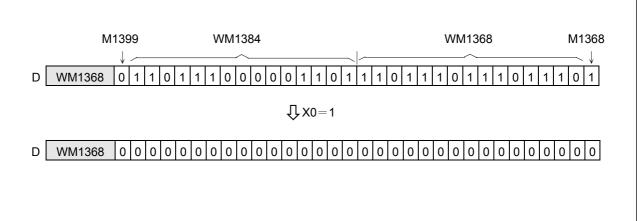

| •     | Reset                                     | (RESET)               | 6-10 |

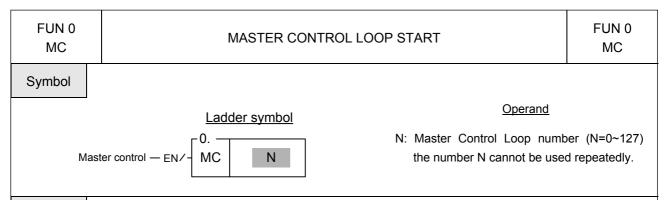

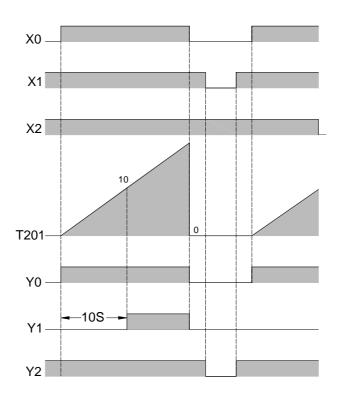

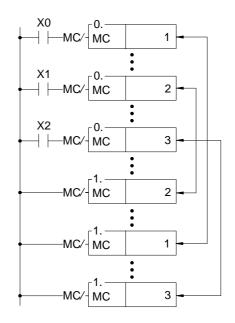

| •     | Master control loop start                 | (FUN0)                | 6-12 |

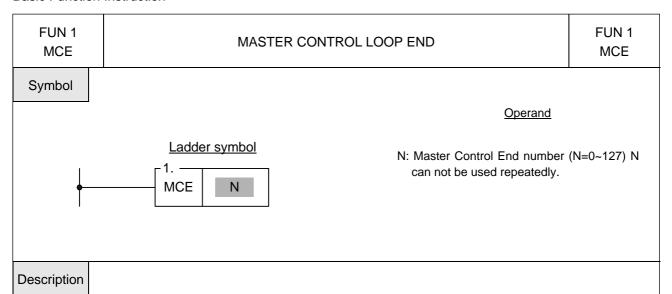

| •     | Master control loop end                   | (FUN01)               | 6-14 |

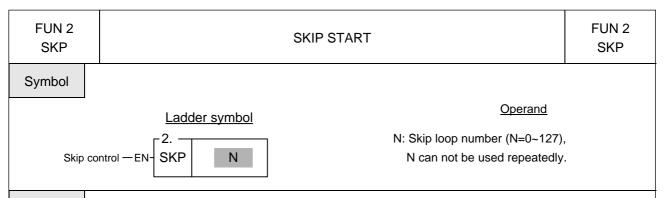

| •     | Skip start                                | (FUN02)               | 6-15 |

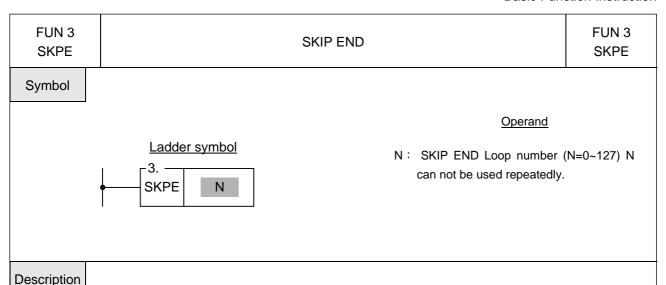

| •     | Skip end                                  | (FUN03)               | 6-17 |

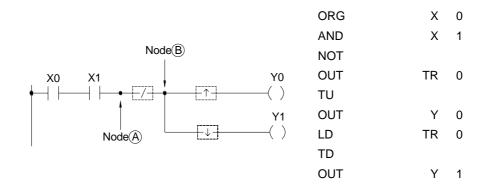

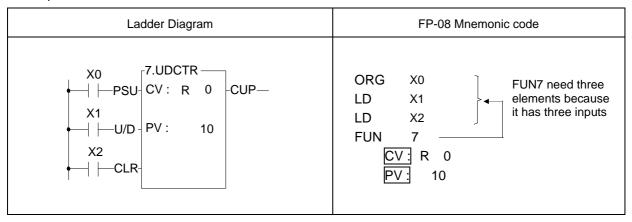

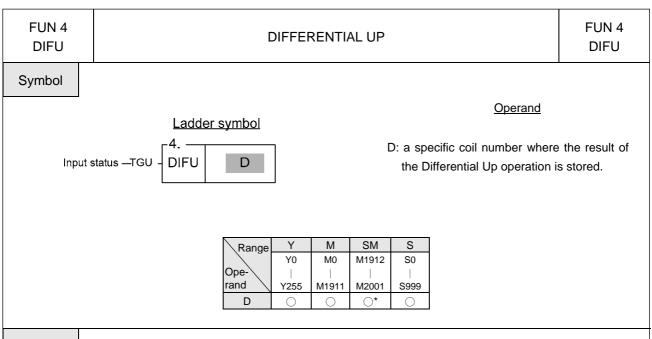

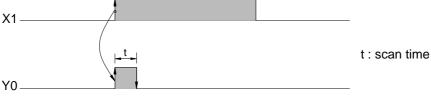

| •     | Differential up                           | (FUN04)               | 6-18 |

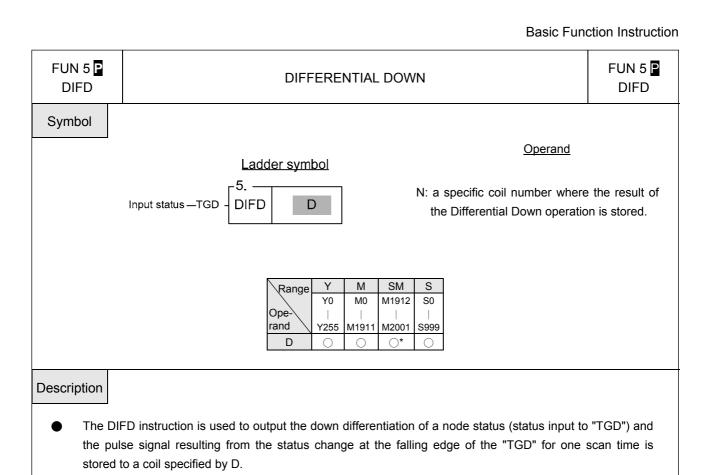

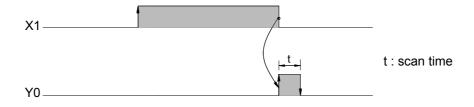

| •     | Differential down                         | (FUN05)               | 6-19 |

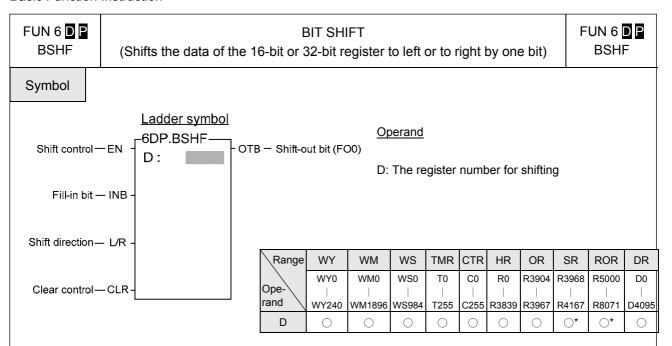

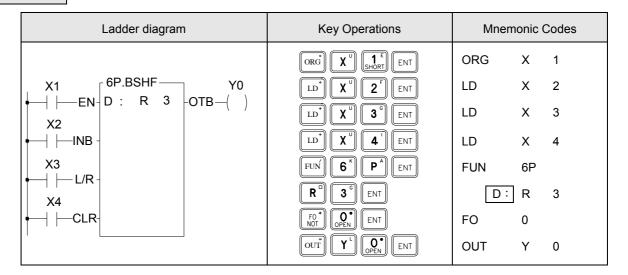

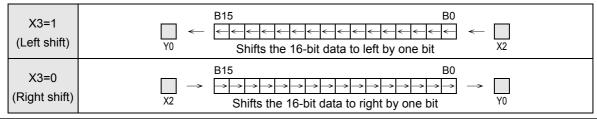

| •     | Bit shift                                 | (FUN06)               | 6-20 |

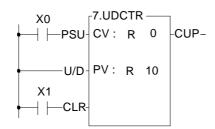

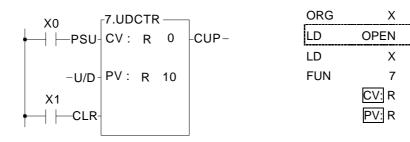

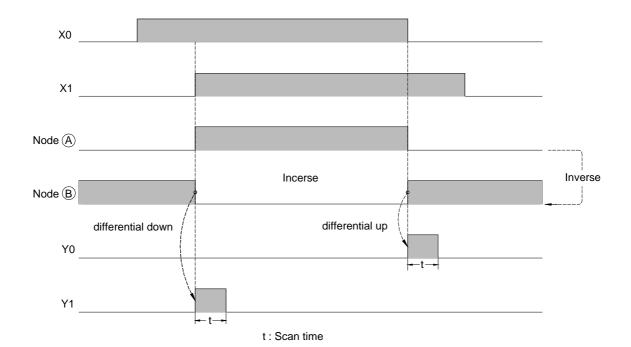

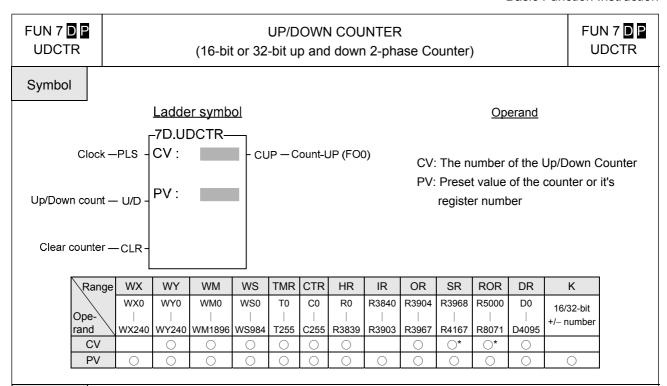

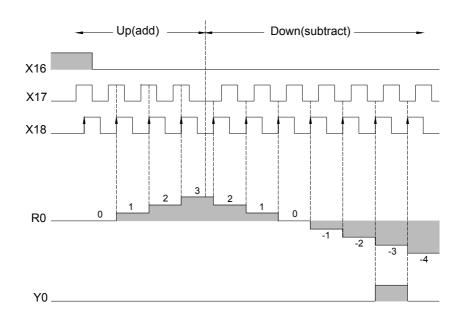

| •     | Up/down counter                           | (FUN07)               | 6-21 |

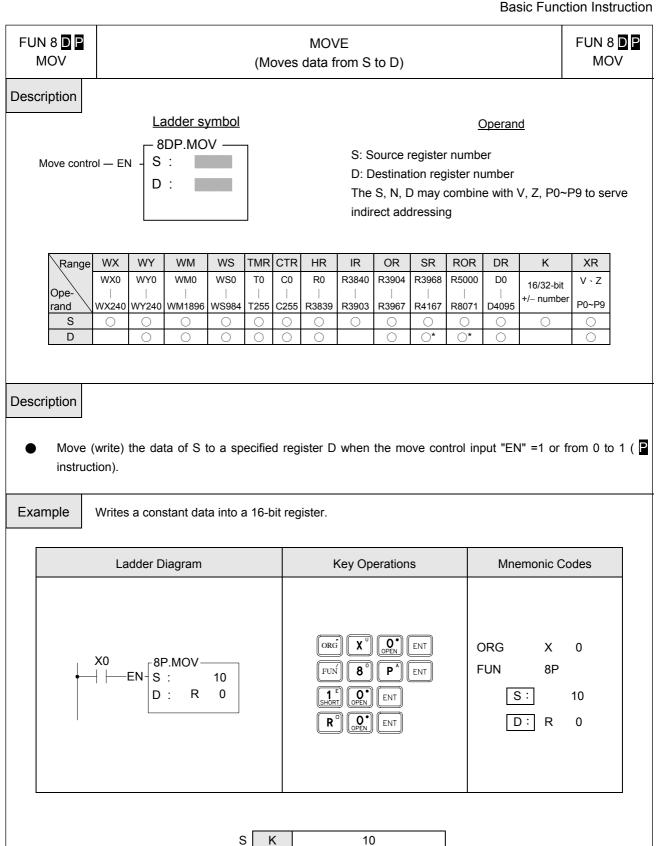

| •     | Move                                      | (FUN08)               | 6-23 |

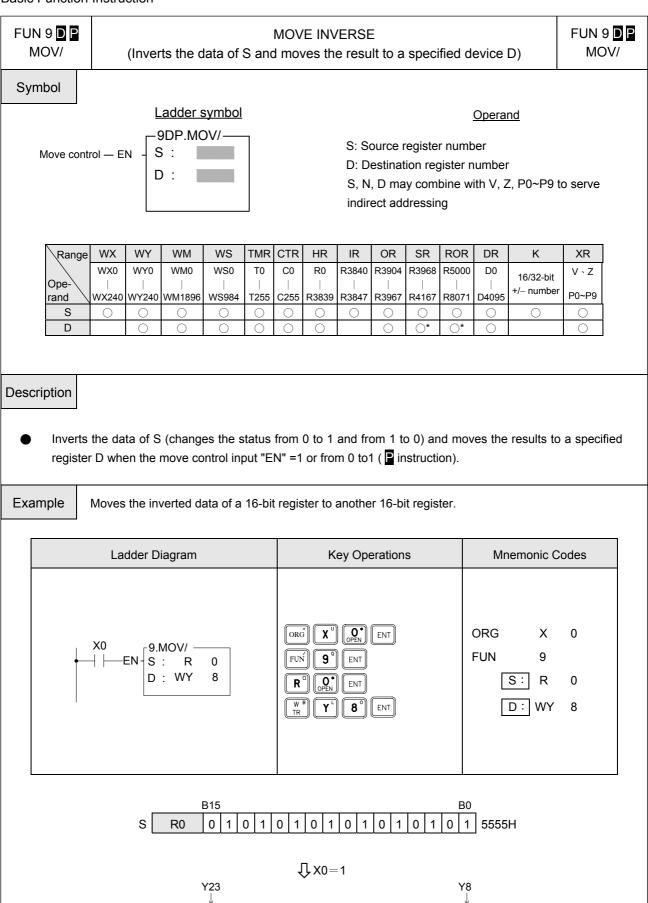

| •     | Move inverse                              | (FUN09)               | 6-24 |

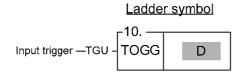

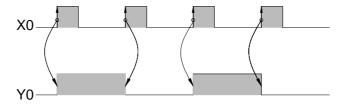

| •     | Toggle switch                             | (FUN10)               | 6-25 |

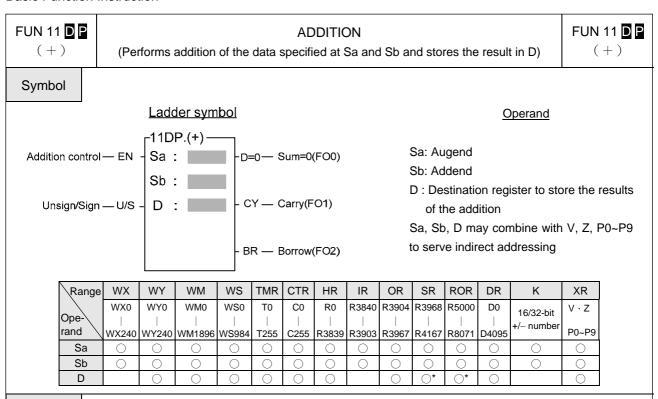

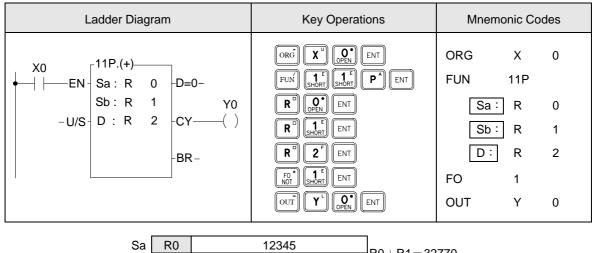

| •     | Addition                                  |                       |      |

|       | Addition                                  | (FUN11)               | 6-26 |

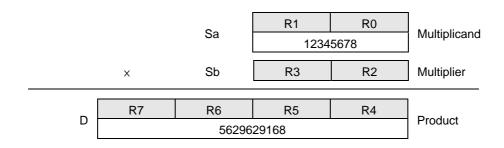

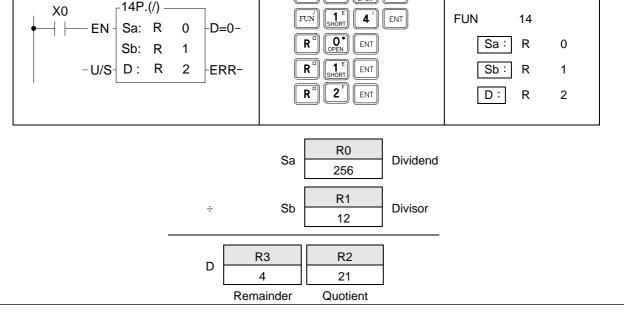

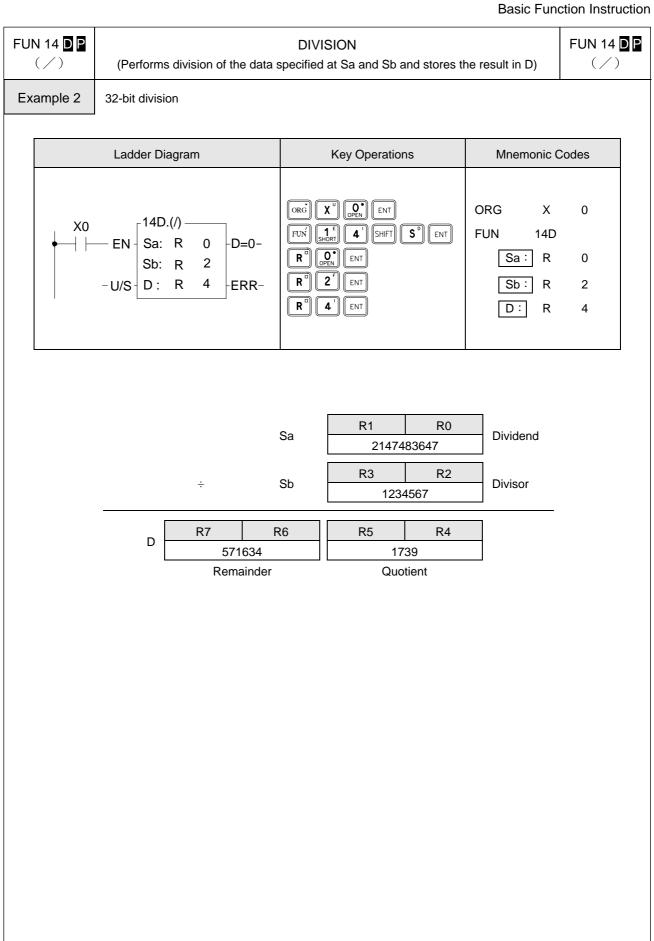

| •    | Division                                             | (FUN14)           | . 6-30  |

|------|------------------------------------------------------|-------------------|---------|

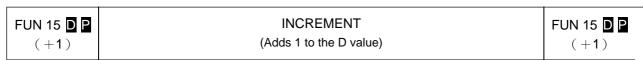

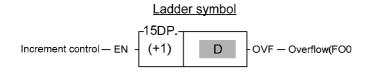

| •    | Increment                                            | (FUN15)           | . 6-32  |

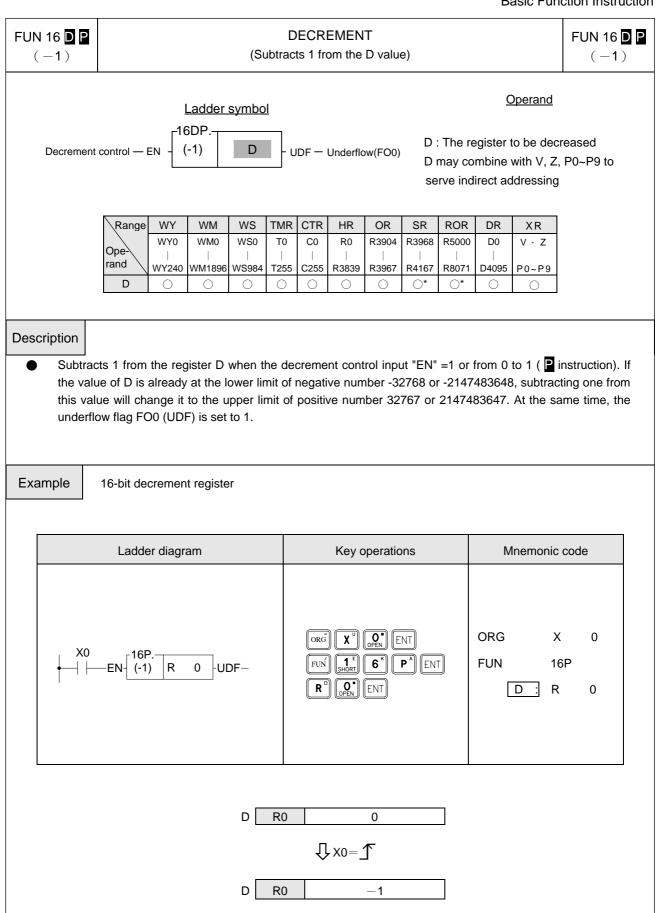

| •    | Decrement                                            | (FUN16)           | . 6-33  |

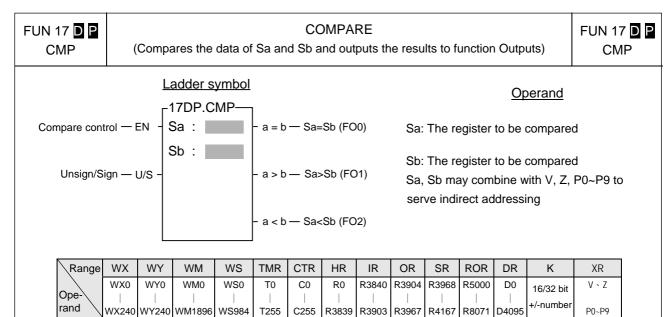

| •    | Compare                                              | (FUN17)           | . 6-34  |

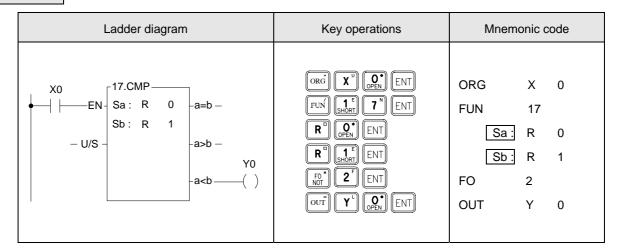

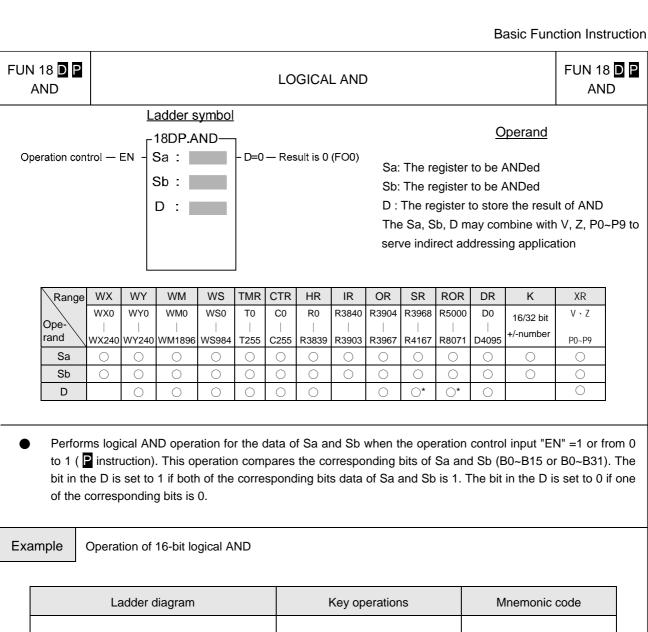

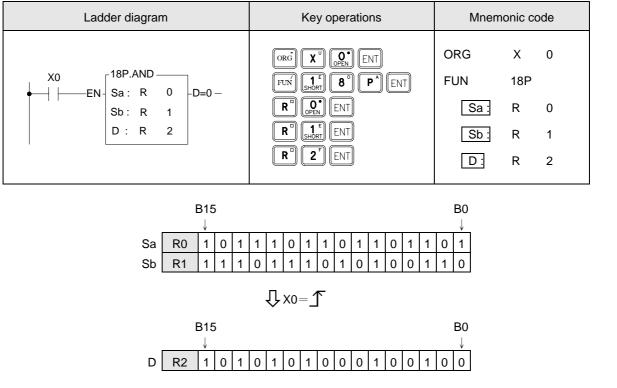

| •    | Logical and                                          | (FUN18)           | . 6-35  |

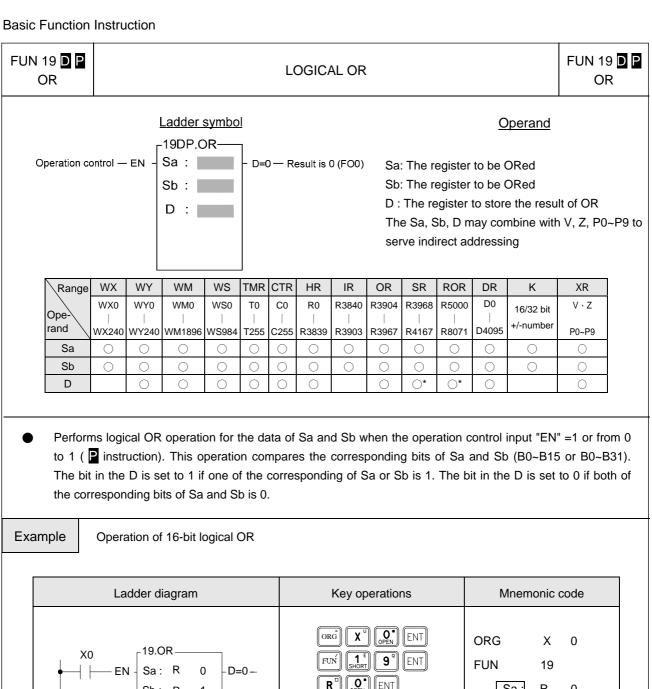

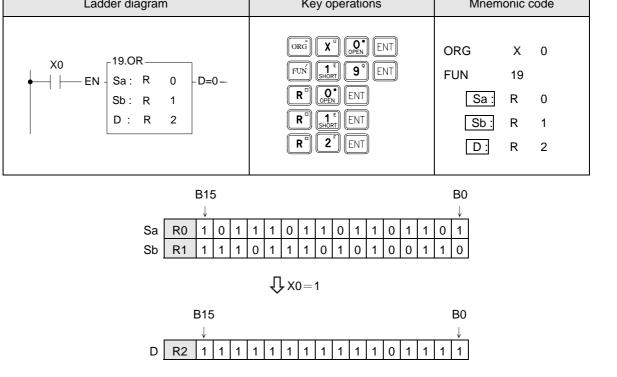

| •    | Logical or                                           | (FUN19)           | . 6-36  |

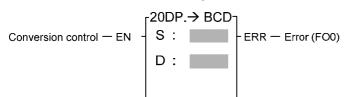

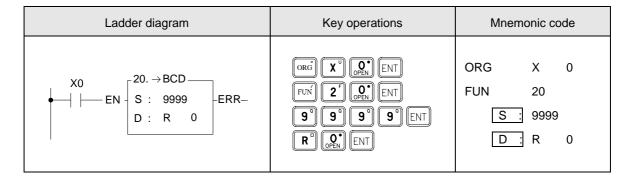

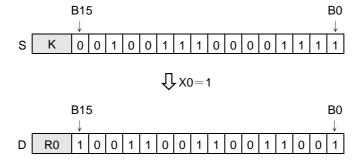

| •    | Binary to bcd conversion                             | (FUN20)           | . 6-37  |

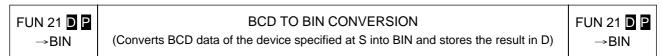

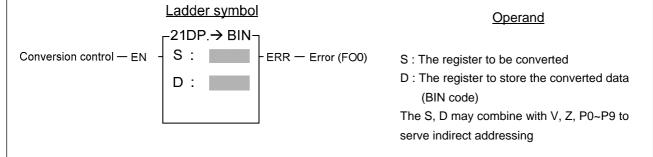

| •    | Bcd to binary conversion                             | (FUN21)           | . 6-38  |

| Chap | ter 7:Advanced Function Inst                         | ructions          |         |

| •    | Flow Control Instructions I                          | (FUN22)           | 7_1     |

|      |                                                      | (FUN23~33)        |         |

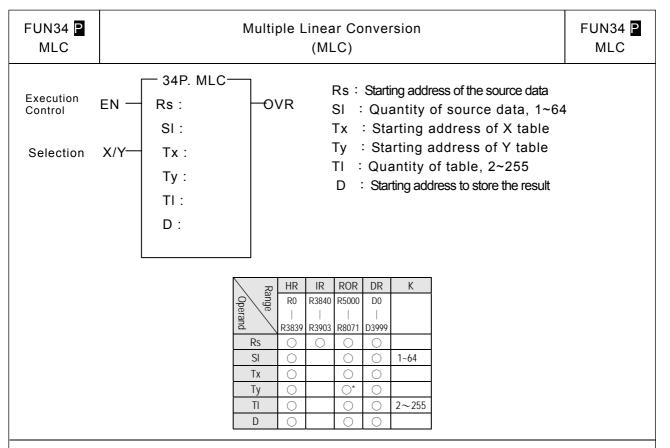

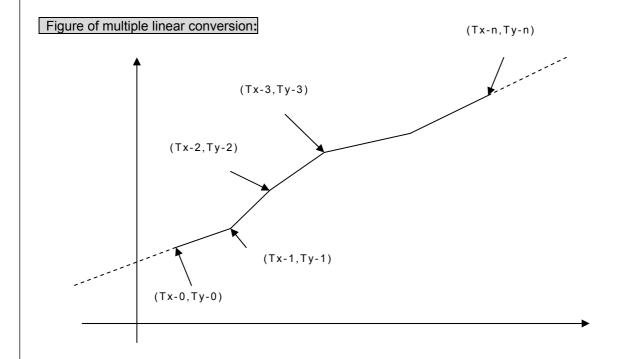

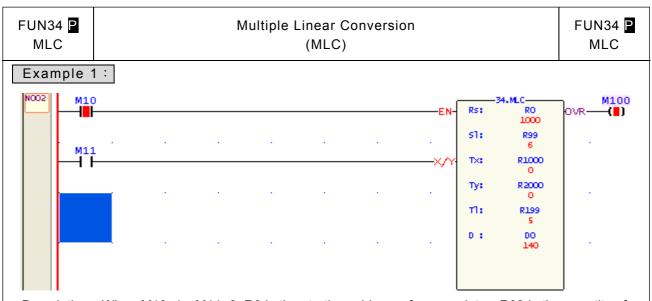

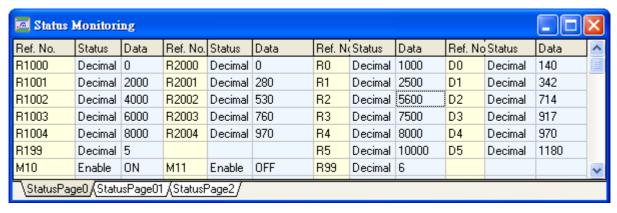

| •    | Arithmetical Operation Instructions                  | (FUN34)           |         |

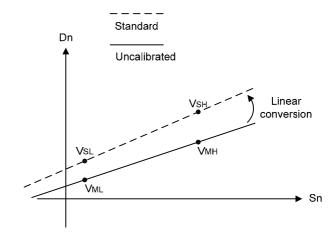

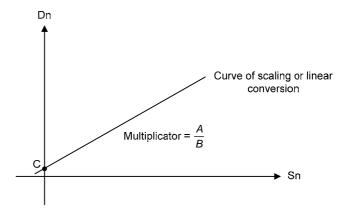

| •    | Multiple Linear Conversion                           | (FUN35~36)        |         |

| •    | Logical Operation Instructions                       | (FUN37)7-28       |         |

| •    | Comparison Instruction  Data Movement Instructions I | ,                 |         |

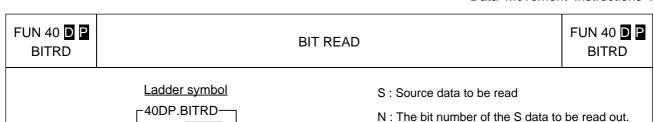

| •    |                                                      | (FUN40~50)7-28    |         |

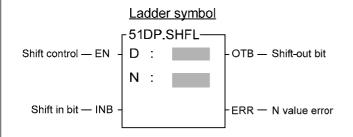

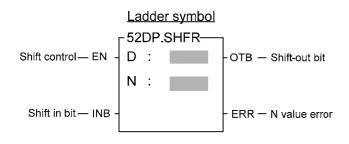

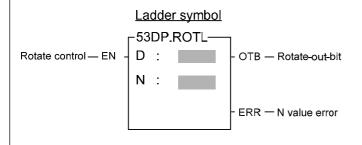

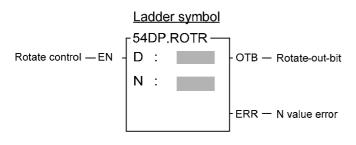

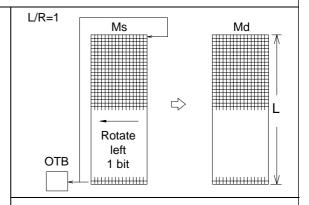

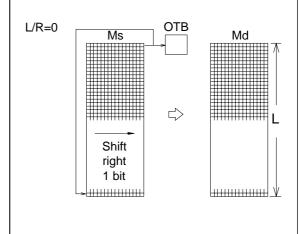

| •    | Shifting / Rotating Instructions                     | (FUN51~54)        |         |

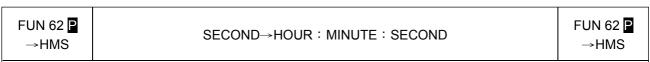

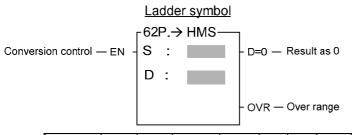

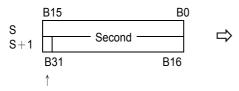

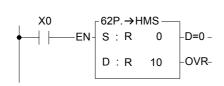

| •    | Code Conversion Instructions                         | (FUN55~64)        |         |

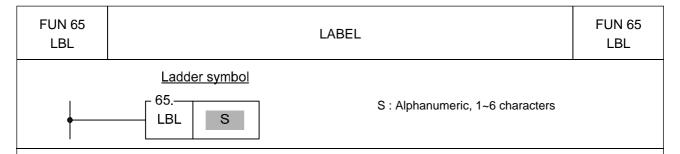

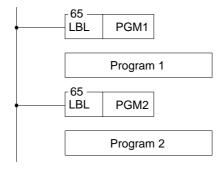

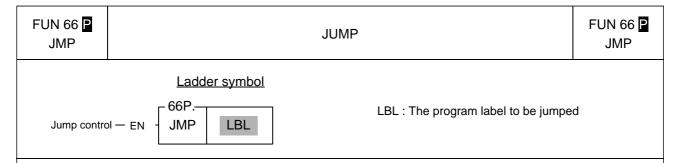

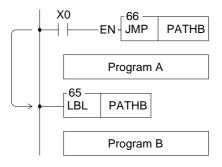

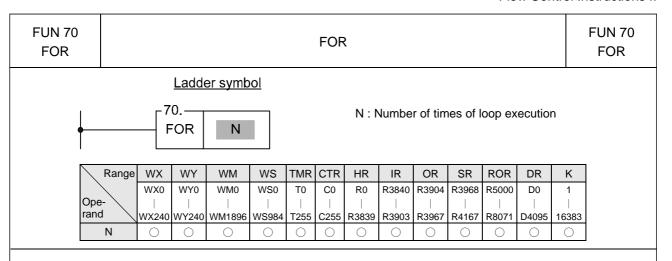

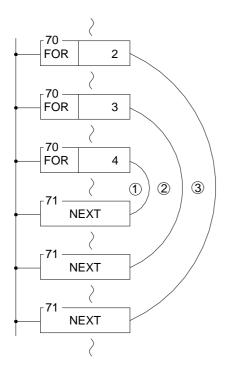

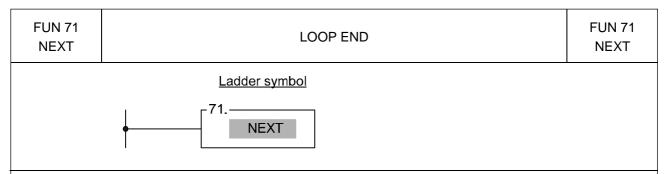

| •    | Flow Control Instructions II                         | (FUN65~71)        |         |

| •    | I / O Instructions I                                 | (FUN74~86)        |         |

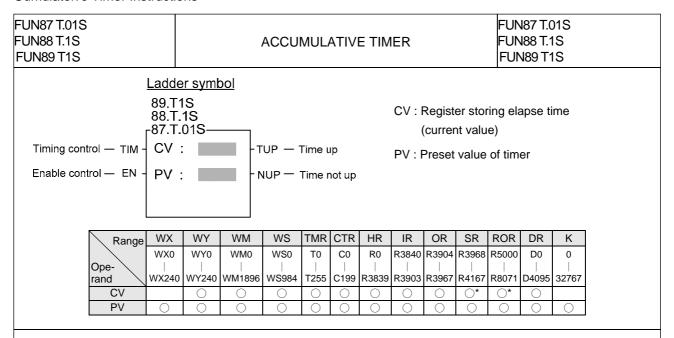

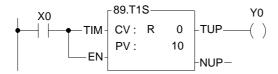

| •    | Cumulative Timer Instructions                        | (FUN87~89)        |         |

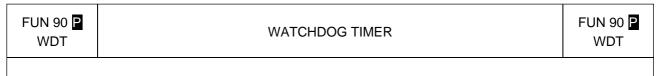

| •    | Watchdog Timer Instructions                          | (FUN90~91)        |         |

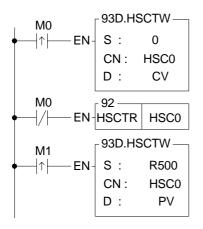

| •    | High Speed Counting / Timing                         | (FUN92~93)        |         |

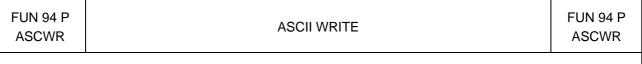

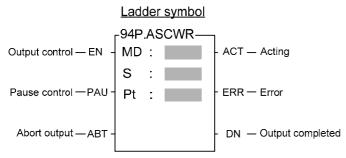

| •    | Report Printing Instructions                         | (FUN94)           |         |

| •    | Slow Up / Slow Down Instructions                     | (FUN95~98)        |         |

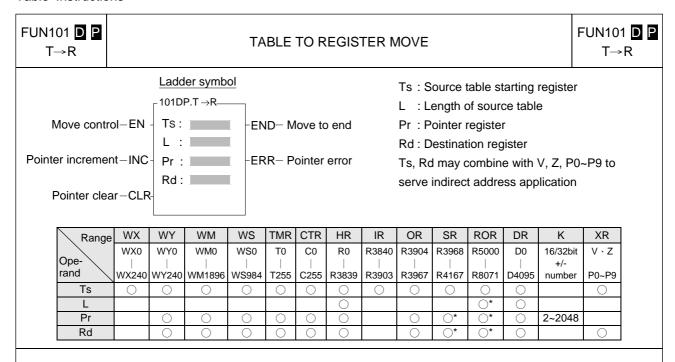

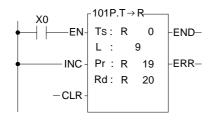

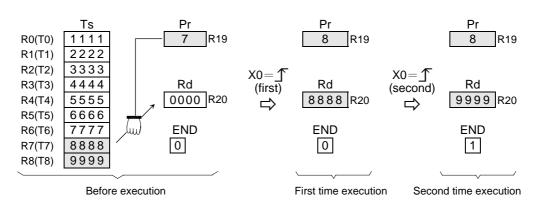

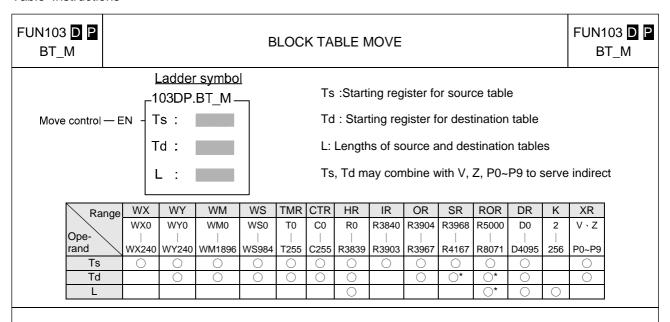

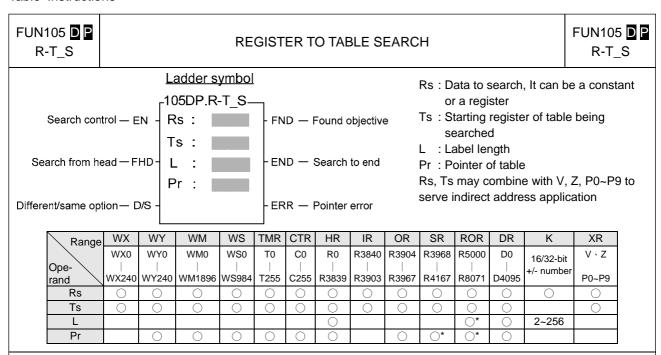

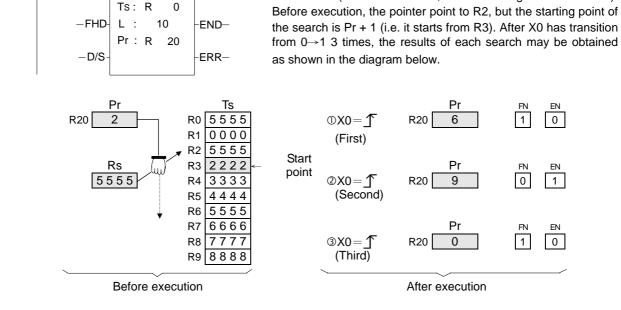

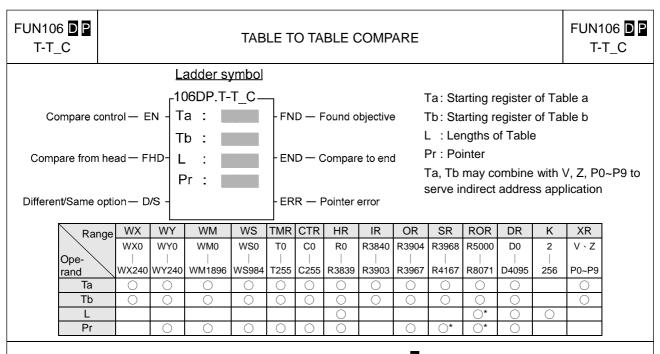

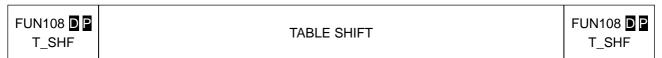

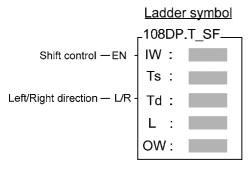

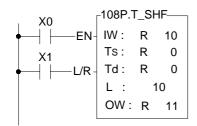

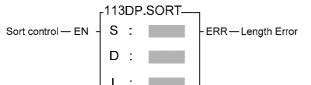

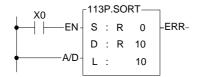

| •    | Table Instructions                                   | (FUN100~114)7-99  |         |

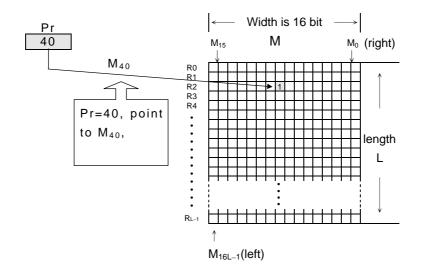

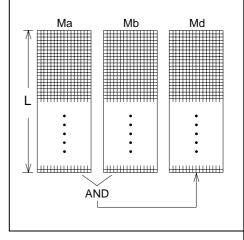

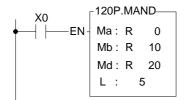

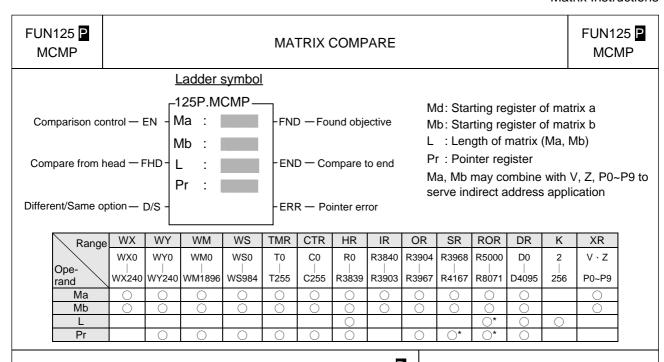

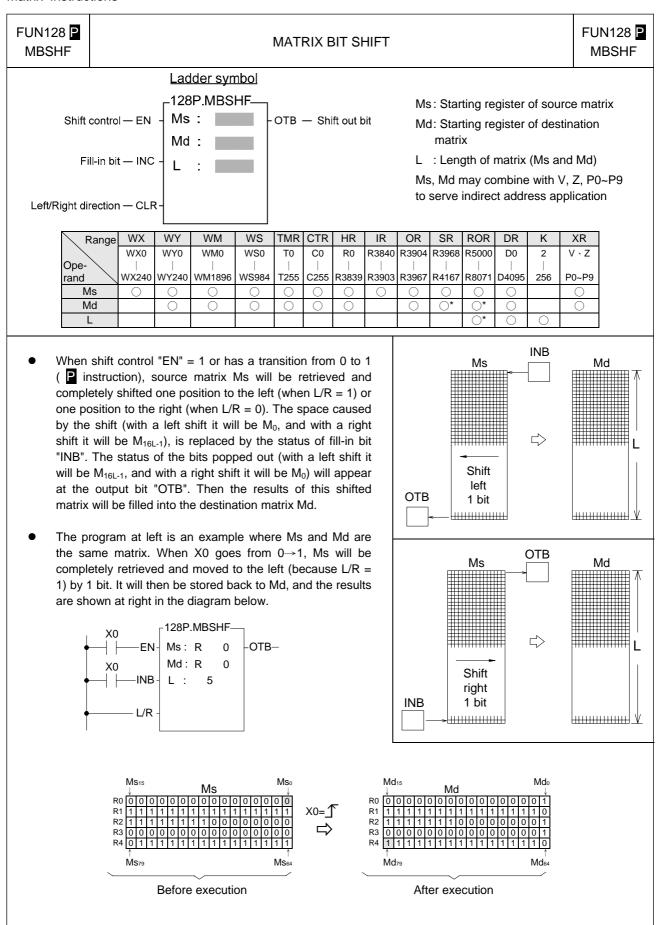

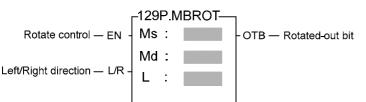

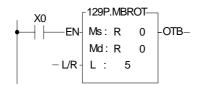

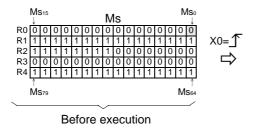

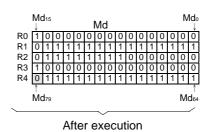

| •    | Matrix Instructions                                  | (FUN120~130)7-118 |         |

| •    | I/O Instruction II                                   | (FUN139)7-130     |         |

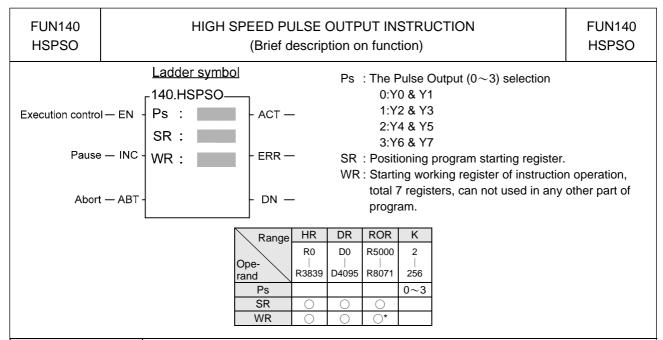

| •    | NC Positioning Instructions I                        | (FUN140~143)7-132 |         |

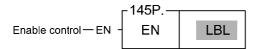

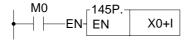

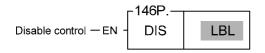

| •    | Enable / Disable Instructions                        | (FUN145~146)7-136 |         |

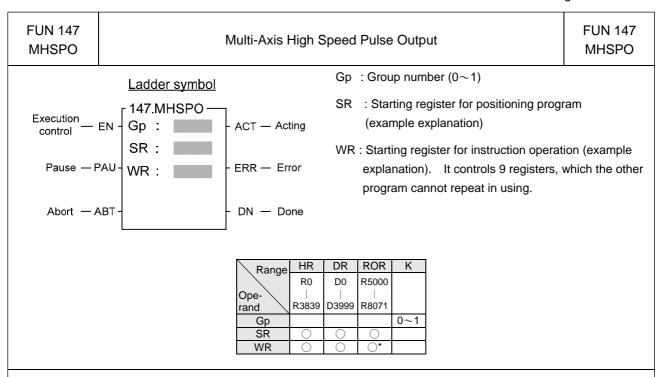

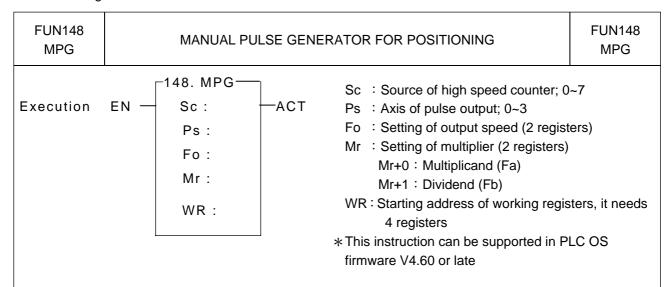

| •    | NC Positioning Instructions II                       | (FUN147~148)7-138 |         |

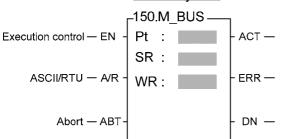

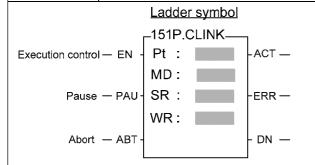

| •    | Communication Instructions                           | (FUN150~151)7-140 |         |

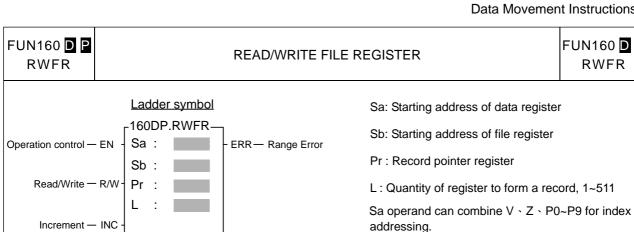

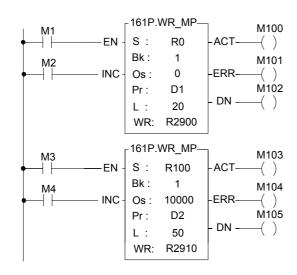

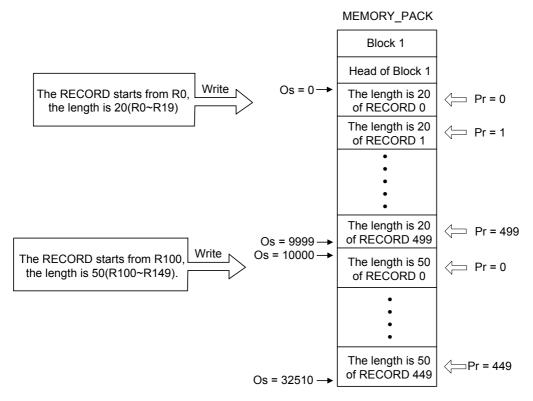

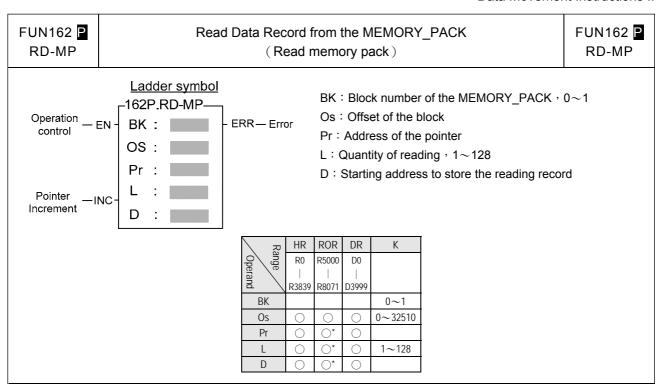

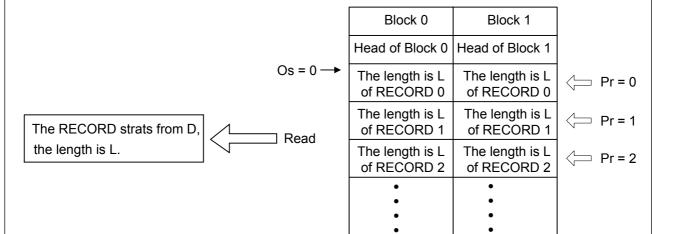

| •    | Data Movement Instructions II                        | (FUN160~162)7-142 |         |

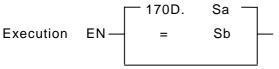

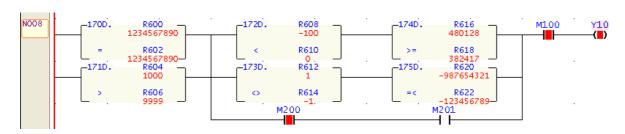

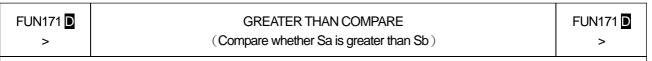

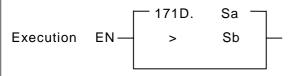

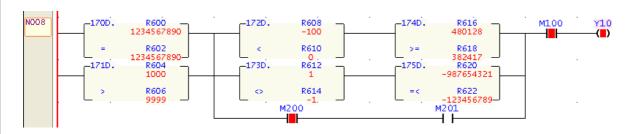

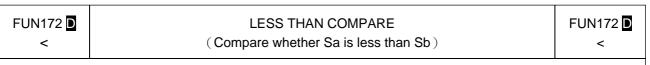

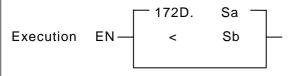

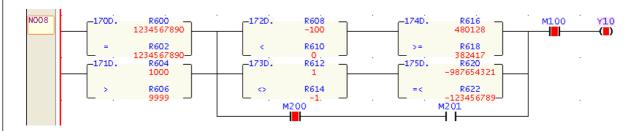

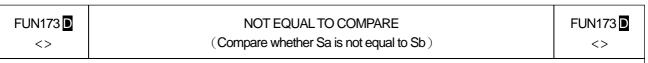

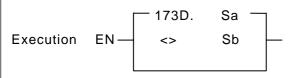

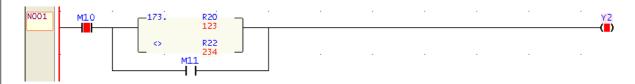

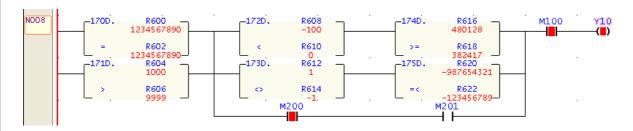

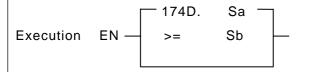

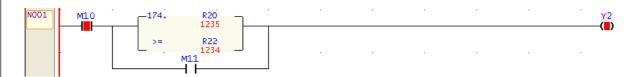

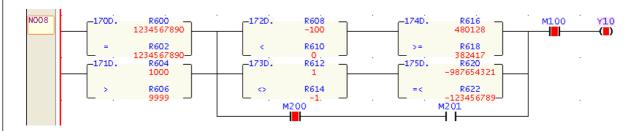

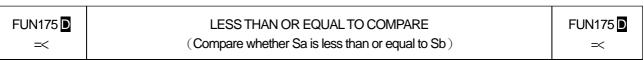

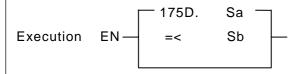

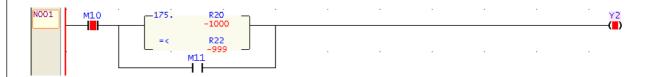

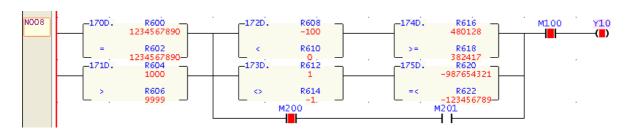

| •    | In Line Comparison Instructions                      | (FUN170~175)7-148 |         |

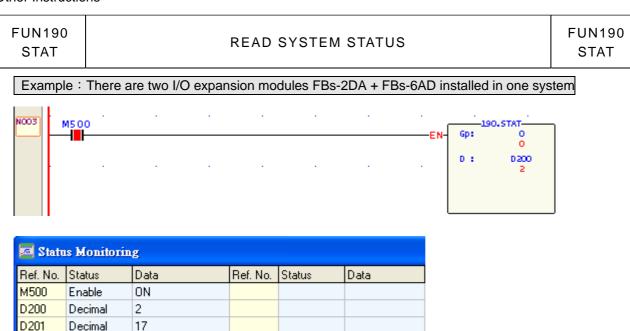

| •    | Other Instructions                                   | (FUN190)7-154     |         |

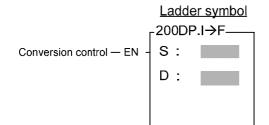

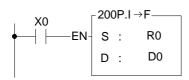

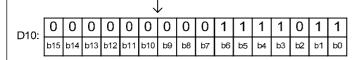

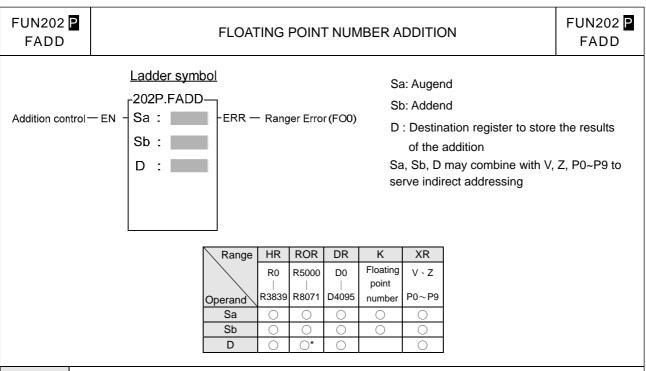

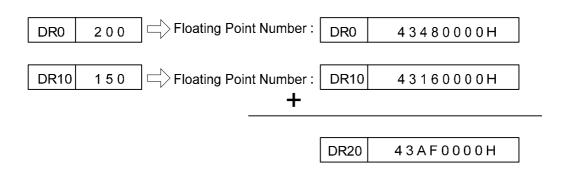

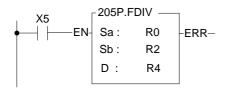

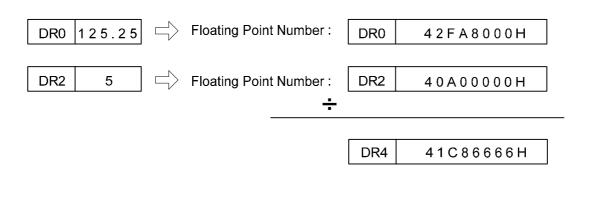

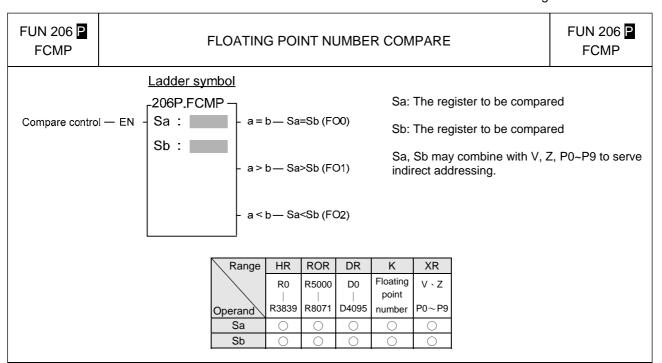

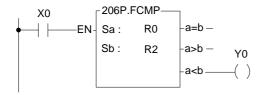

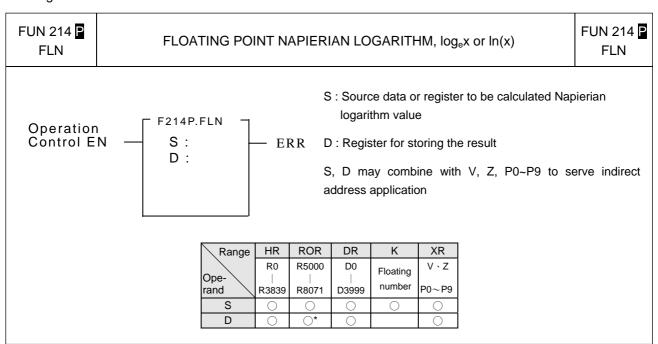

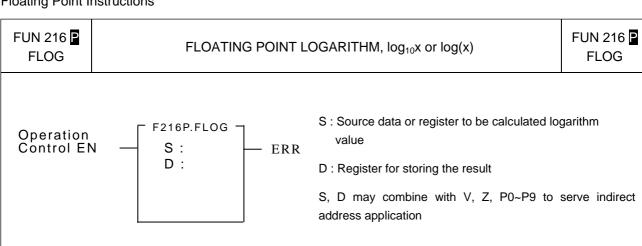

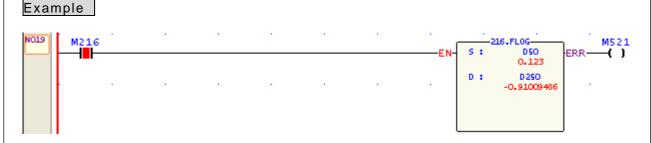

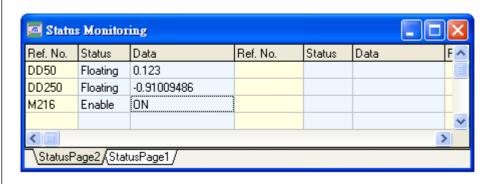

| •    | Floating Point Instructions                          | (FUN200~220)7-156 | ~ 7-177 |

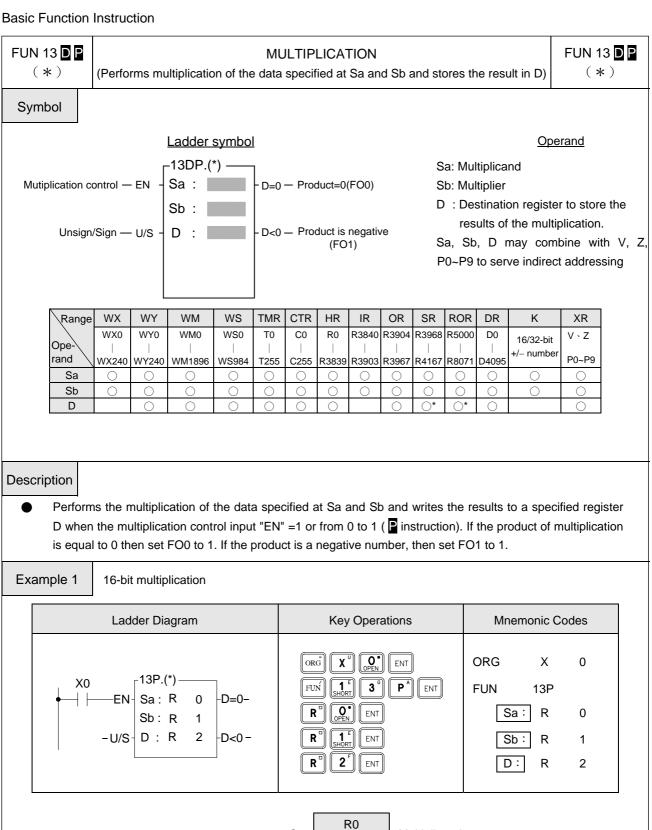

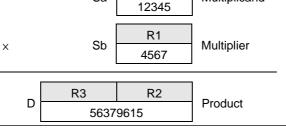

Multiplication

(FUN13) .....6-28

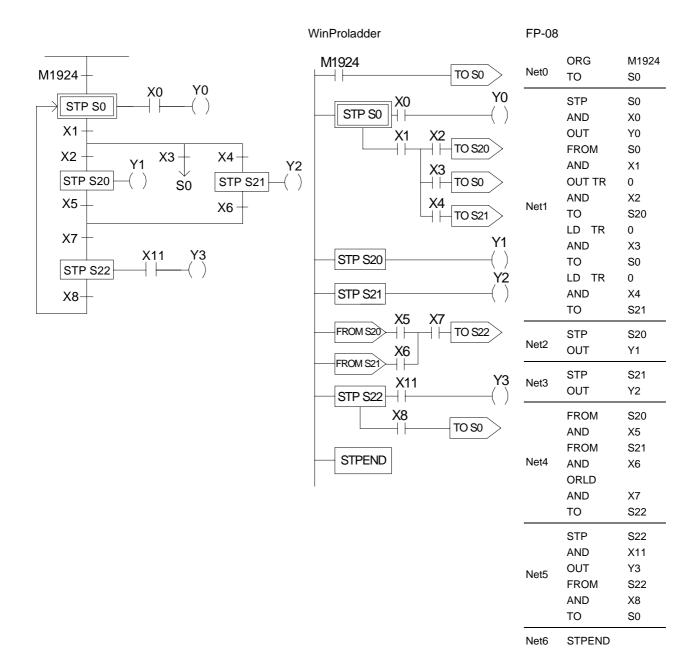

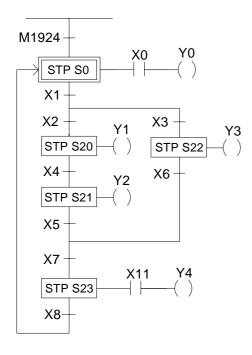

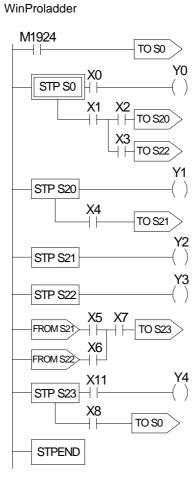

| Chapter 8: Step Instruction Description |  |

|-----------------------------------------|--|

|                                         |  |

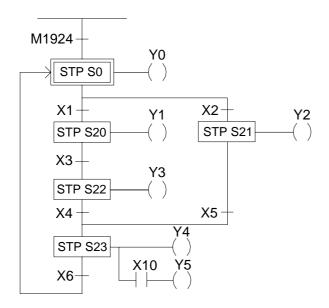

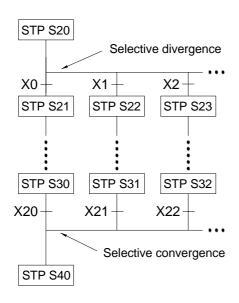

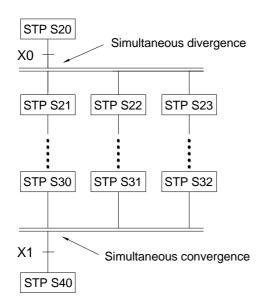

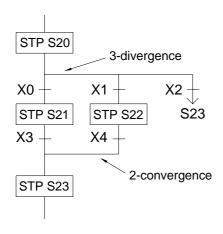

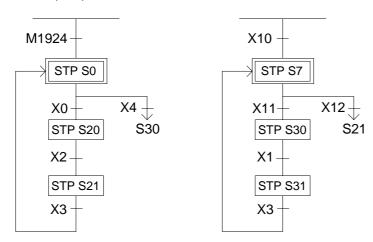

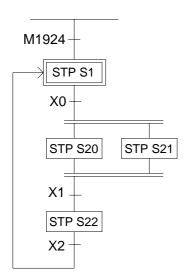

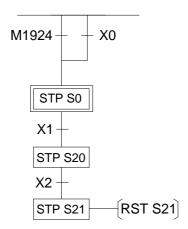

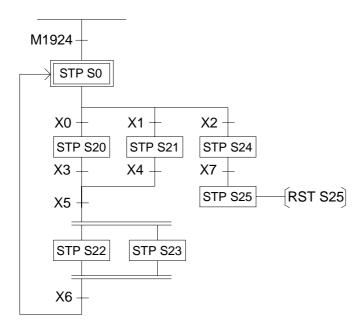

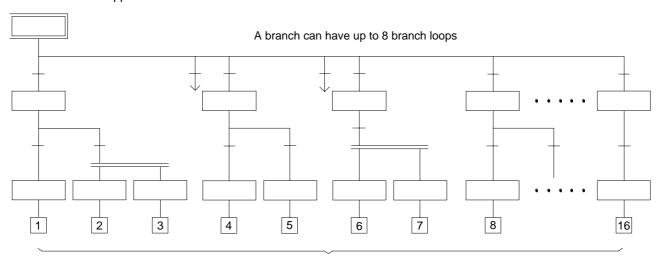

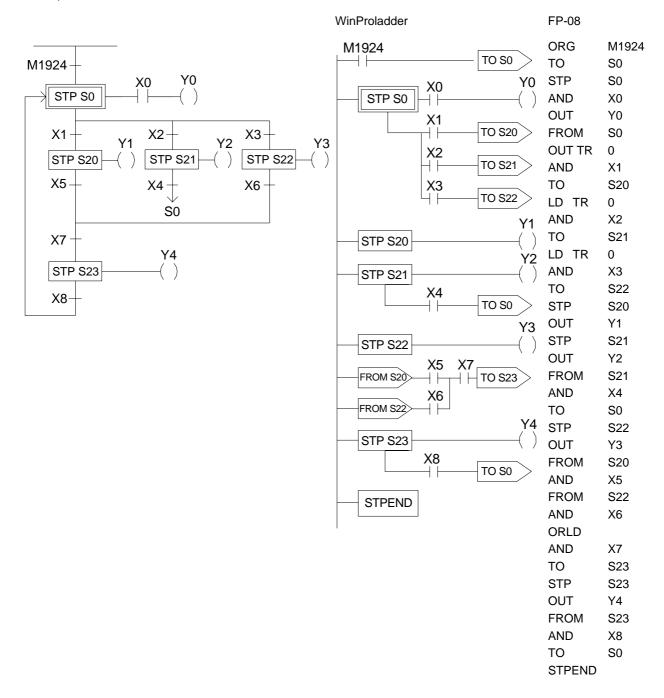

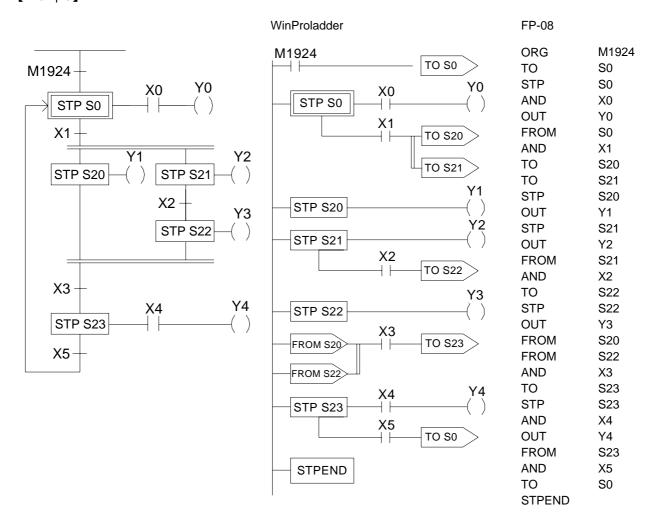

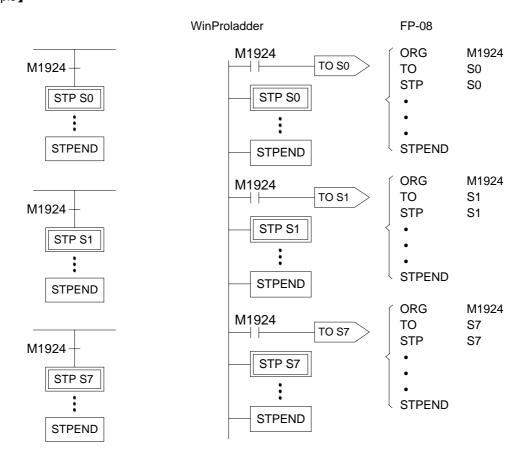

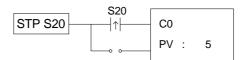

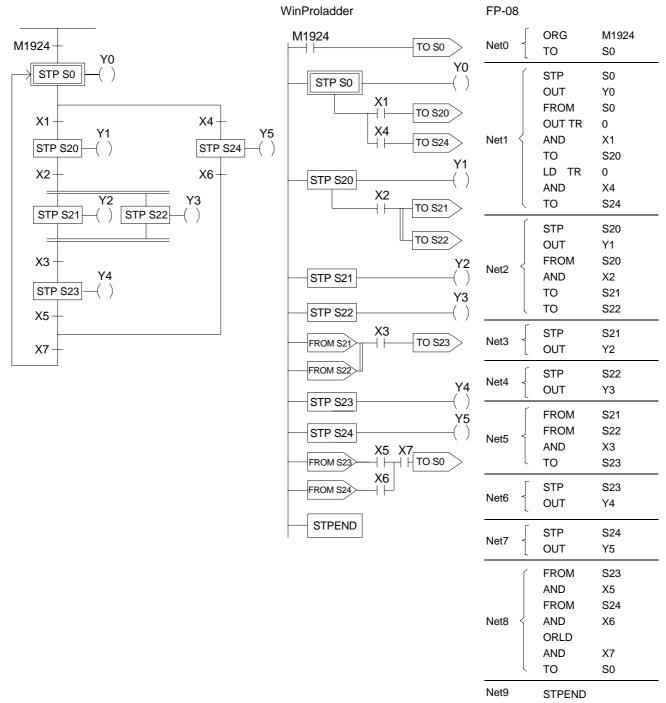

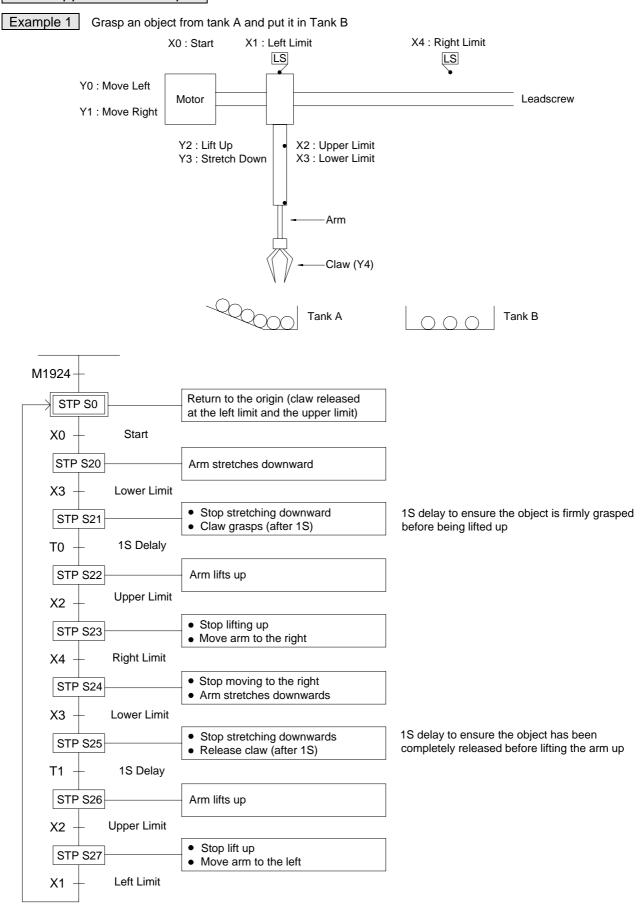

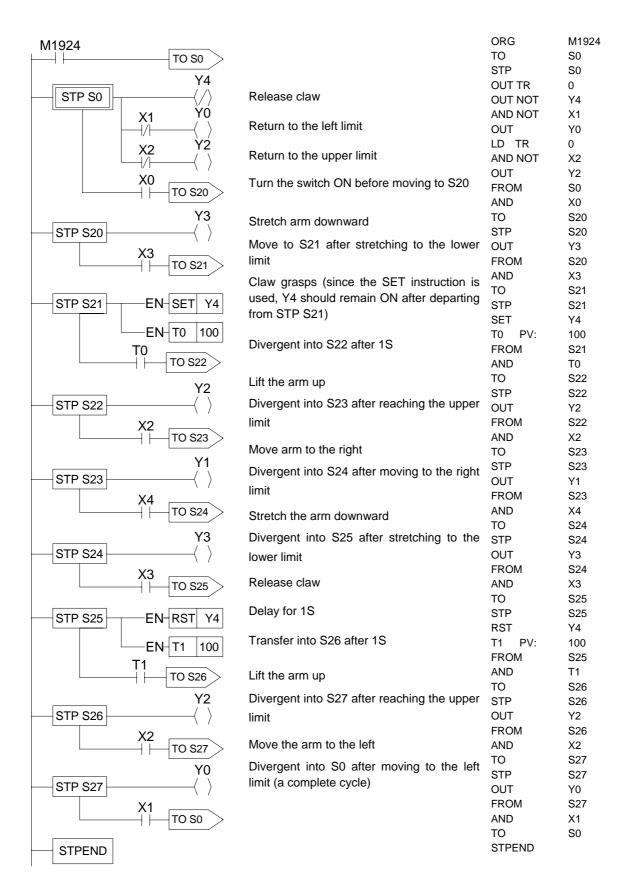

| 8.1         | The Operation Principle of Step Ladder Diagram8-1                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 8.2         | Basic Formation of Step Ladder Diagram                                                                                                        |

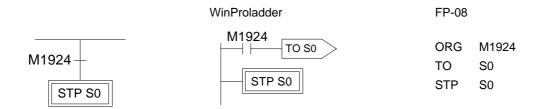

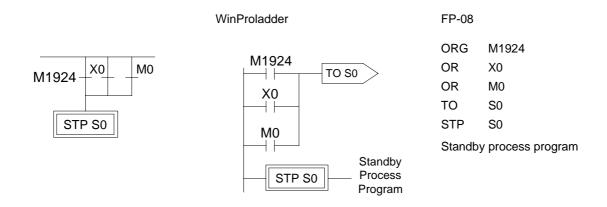

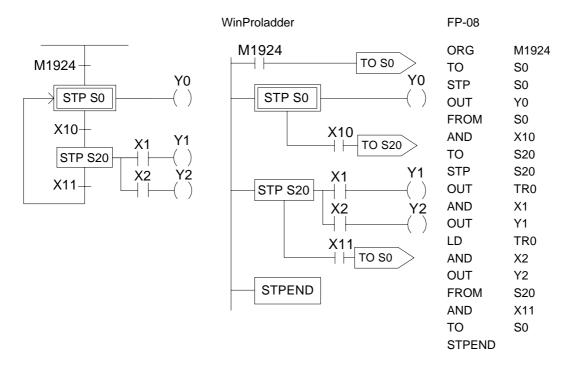

| 8.3         | Instruction of Step Instructions: STP, FROM, TO, and STPEND                                                                                   |

| 8.4         | Notes for Writing a Step Ladder Diagram ······ 8-11                                                                                           |

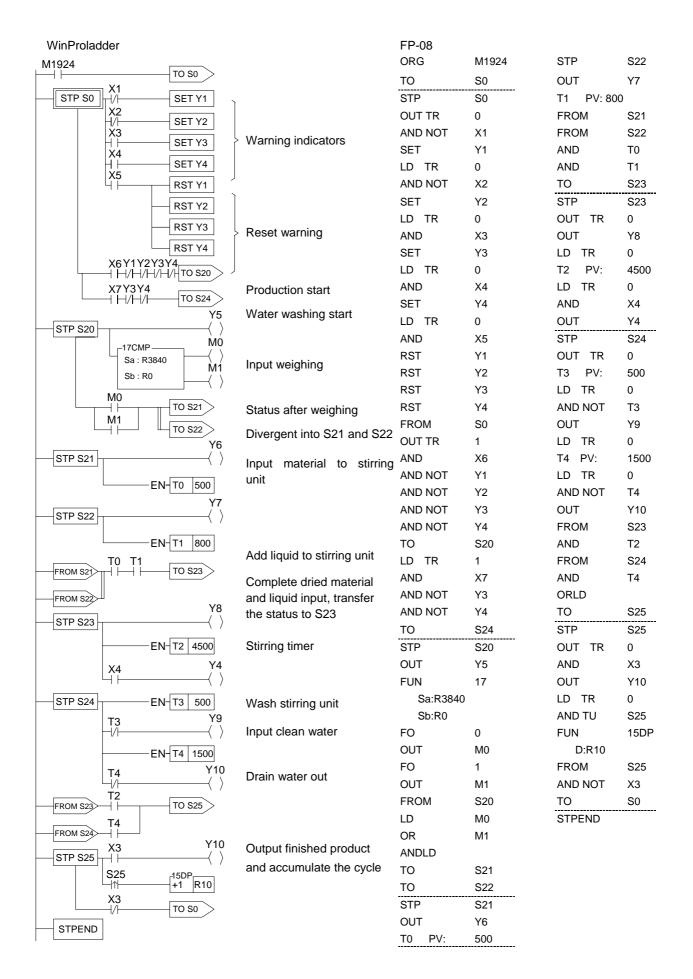

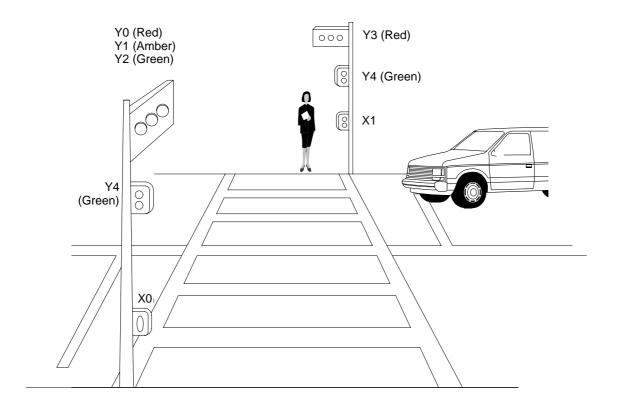

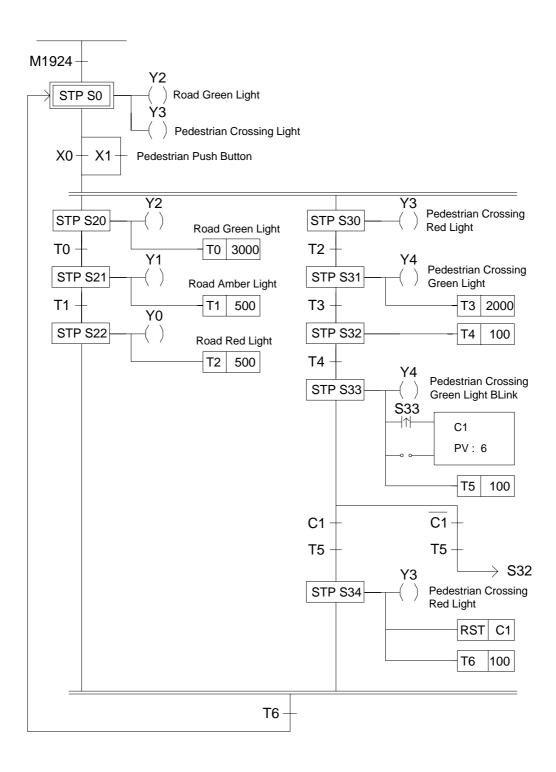

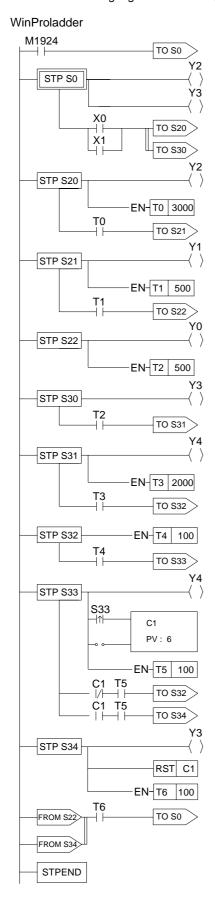

| 8.5         | Application Examples 8-15                                                                                                                     |

| 8.6         | Syntax Check Error Codes for Step Instruction8-22                                                                                             |

|             |                                                                                                                                               |

|             |                                                                                                                                               |

|             |                                                                                                                                               |

| [App        | pendix I ] FBs-PACK Operation Instruction                                                                                                     |

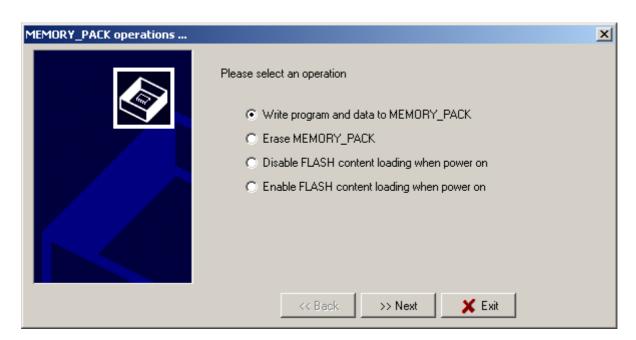

| <b>[App</b> | pendix I FBs-PACK Operation Instruction  Write Ladder Program and Register Data to FBs-PACK with WinProladder                                 |

|             | -                                                                                                                                             |

| 1.1         | Write Ladder Program and Register Data to FBs-PACK with WinProladder Write Ladder Program and Register Data to FBs-PACK with Special Register |

## [Instruction]

## Chapter 1 PLC Ladder Diagram and the Coding Rules of Mnemonic

In this chapter, we would like to introduce you the basic principles of ladder diagram, in addition, the coding rules of Mnemonic will be introduced as well, it's essential for the user who use FP-08 as a programming tool. If you are familiar with PLC Ladder Diagram and mnemonic coding rules, you may skip this chapter.

## 1.1 The Operation Principle of Ladder Diagram

Ladder Diagram is a type of graphic language for automatic control systems it had been used for a long period since World War II. Until today, it is the oldest and most popular language for automatic control systems. Originally there are only few basic elements available such as A-contact (Normally ON), B contact (Normally OFF), output Coil, Timers and Counters. Not until the appearance of microprocessor based PLC, more elements for Ladder Diagram, such as differential contact, retentive coil (refer to page 1-6) and other instructions that a conventional system cannot provide, became available.

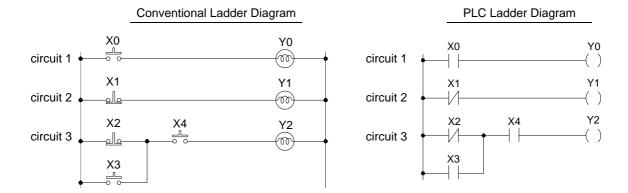

The basic operation principle for both conventional and PLC Ladder Diagram is the same. The main difference between the two systems is that the appearance of the symbols for conventional Ladder Diagram are more closer to the real devices, while for PLC system, symbols are simplified for computer display. There are two types of logic system available for Ladder Diagram logic, namely combination logic and sequential logic. Detailed explanations for these two logics are discussed below.

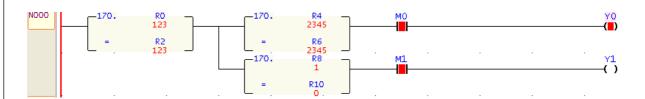

## 1.1.1 Combination Logic

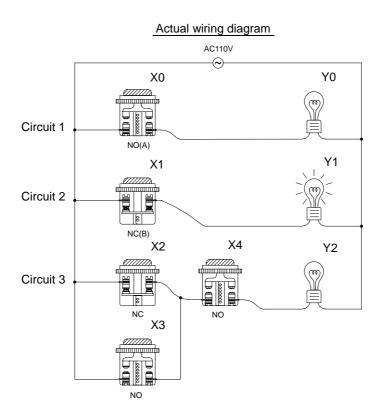

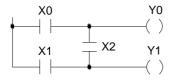

Combination logic of the Ladder Diagram is a circuit that combines one or more input elements in series or parallel and then send the results to the output elements, such as Coils, Timers/Counters, and other application instructions.

The above example illustrated the combination logic using the actual wiring diagram, conventional Ladder Diagram, and PLC Ladder Diagram. Circuit 1 uses a NO (Normally Open) switch that is also called "A" switch or contact. Under normal condition (switch is not pressed), the switch contact is at OFF state and the light is off. If the switch is pressed, the contact status turns ON and the light is on. In contrast, circuit 2 uses a NC (Normally Close) switch that is also called "B" switch or contact. Under normal condition, the switch contact is at ON state and the light is on. If the switch is pressed, the contact status turns OFF and the light also turns off.

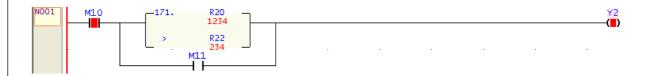

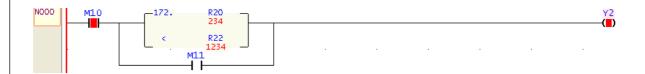

Circuit 3 contains more than one input element. Output Y2 light will turn on under the condition when X2 is closed or X3 switches to ON, and X4 must switch ON too.

### 1.1.2 Sequential Logic

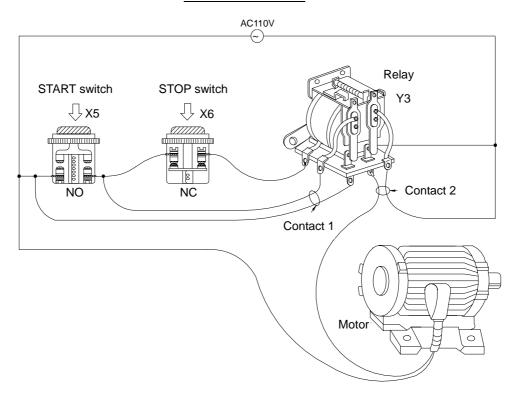

The sequential logic is a circuit with feedback control; that is, the output of the circuit will be feedback as an input to the same circuit. The output result remains in the same state even if the input condition changes to the original position. This process can be best explained by the ON/OFF circuit of a latched motor driver as shown in below.

#### Actual wiring diagram

####

When we first connect this circuit to the power source, X6 switch is ON but X5 switch is OFF, therefore the relay Y3 is OFF. The relay output contacts 1 and 2 are OFF because they belong to A contact (ON when relay is ON). Motor does not run. If we press down the switch X5, the relay turns ON as well as contacts 1 and 2 are ON and the Motor starts. Once the relay turns ON, if we release the X5 switch (turns OFF), relay can retain its state with the feedback support from contact 1 and it is called Latch Circuit. The following table shows the switching process of the example we have discussed above.

|            | X5 switch<br>(NO) | X6 switch (NC) | Motor (Relay) status |

|------------|-------------------|----------------|----------------------|

| ①          | Released          | Released       | OFF                  |

| 2          | Pressed           | Released       | ON                   |

| 3          | Released          | Released       | ON                   |

| <b>↓ ④</b> | Released          | Pressed        | OFF                  |

| ↓<br>⑤     | Released          | Released       | OFF                  |

From the above table we can see that under different stages of sequence, the results can be different even the input statuses are the same. For example, let's take a look at stage ① and stage ③ , X5 and X6 switches are both released, but the Motor is ON (running) at stage ③ and is OFF (stopped) at stage ① . This sequential control with the feedback of the output to the input is a unique characteristic of Ladder Diagram circuit. Sometimes we call the Ladder Diagram a "Sequential Control Circuit" and the PLC a "Sequencer". In this section, we only use the A/B contacts and output coils as the example. For more details on sequential instructions please refer to chapter 5 - "Introduction to Sequential Instructions."

## 1.2 Differences Between Conventional and PLC Ladder Diagram

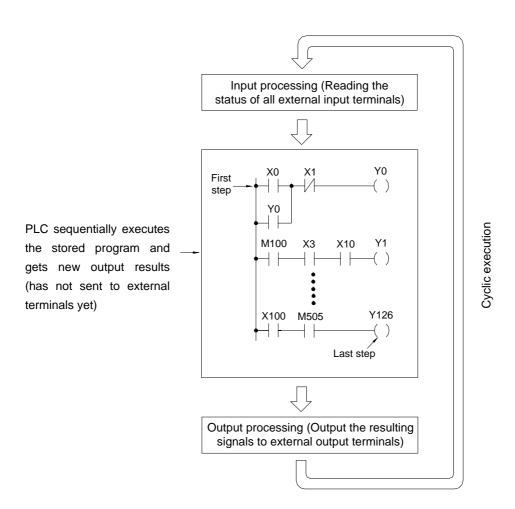

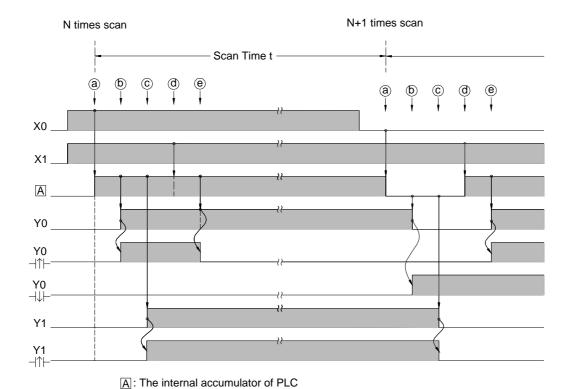

Although the basic operation principle for both conventional and PLC Ladder Diagram are the same, but in reality, PLC uses the CPU to emulate the conventional Ladder Diagram operations; that is, PLC uses scanning method to monitor the statuses of input elements and output coils, then uses the Ladder Diagram program to emulate the results which are the same as the results produced by the conventional Ladder Diagram logic operations. There is only one CPU, so the PLC has to sequentially examine and execute the program from its first step to the last step, then returns to the first step again and repeats the operation (cyclic execution). The duration of a single cycle of this operation is called the scan time. The scan time varies with the program size. If the scan time is too long, then input and output delay will occur. Longer delay time may cause big problems in controlling fast response systems. At this time, PLCs with short scan time are required. Therefore, scan time is an important specification for PLCs. Due to the advance in microcomputer and ASIC technologies nowadays the scan speed has been enhanced a great deal. A typical FB<sub>E</sub>-PLC takes approximately 0.33 ms for IK steps of contact. The following diagram illustrates the scanning process of a PLC Ladder Diagram.

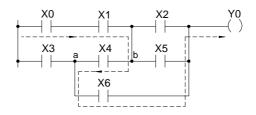

Besides the time scan difference mentioned above, the other difference between the conventional and PLC Ladder Diagram is "Reverse flow" characteristic. As shown in the diagram below, if X0, X1, X4 and X6 are ON, and the remaining elements are OFF. In a conventional Ladder Diagram circuit, a reverse flow route for output Y0 can be defined by the dashed line and Y0 will be ON. While for PLC, Y0 is OFF because the PLC Ladder Diagram scans from left to right, if X3 is off then CPU believes node "a" is OFF, although X4 and node "b" are all ON, since the PLC scan reaches X3 first. In other words, the PLC ladder can only allow left to right signal flow while conventional ladder can flow bi-directional.

#### Reverse flow of conventional Ladder diagram

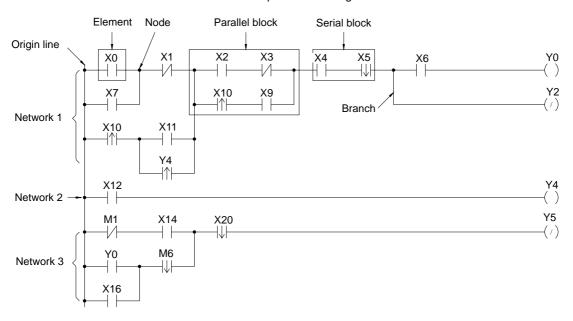

## 1.3 Ladder Diagram Structure and Terminology

#### Sample Ladder Diagram

(Remark: The maximum size of FBs-PLC network is 16 rows × 22 columns)

As shown above, the Ladder Diagram can be divided into many small cells. There are total 88 cells (8 rows X 11 columns) for this example Ladder Diagram. One cell can accommodate one element. A completed Ladder Diagram can be formed by connecting all the cells together according to the specific requirements. The terminologies related to Ladder Diagram are illustrated below.

#### ① Contact

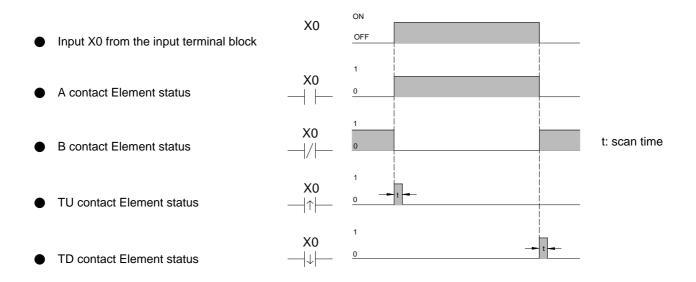

Contact is an element with open or short status. One kind of contact is called "Input contact" (reference number prefix with X) and its status reference from the external signals (the input signal comes from the input terminal block). Another one is called "Relay contact" and its status reflects the status of relay coil (please refer to ②). The relation between the reference number and the contact status depends on the contact type. The contact elements provided by FB series PLC include: A contact, up/down differential (TU/TD) contacts and Open/Short contacts. Please refer to ④ for more details.

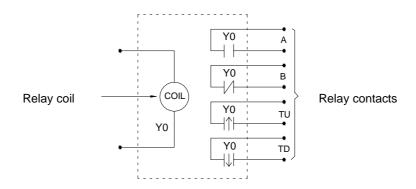

#### 2 Relay

Same as the conventional relay, it consists of a Coil and a Contact as shown in the diagram below.

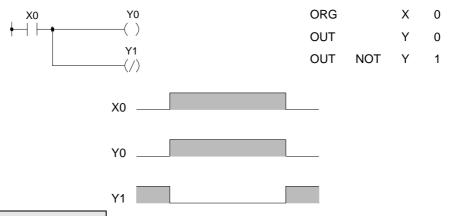

We must energize the coil of relay first (using OUT instruction) in order to turn on the relay. After the coil is energized, its contact status will be ON too. As shown in the example above, if Y0 turns ON, then the relay contact A is ON and contact B is OFF, TU contact only turns ON for one scan duration and TD contact is OFF. If Y0 turns OFF, then the relay contact A is ON and contact B is ON, TU contact is OFF and TD contact only turns ON for one scan duration (Please refer to chapter 4 "Introduction to Sequential Instructions" for operations of A,B,TU and TD contacts).

There are four types of FB-PLC relays, namely  $Y \triangle \triangle \triangle$  (output relay),  $M \triangle \triangle \triangle \triangle$  (internal relay),  $S \triangle \triangle \triangle$  (step relay) and  $TR \triangle \triangle$  (temporary relay). The statuses of output relays will be sent to the output terminal block.

- ③ Origin-line: The starting line at the left side of the Ladder Diagram.

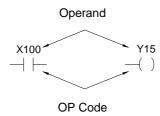

- ④ Element: Element is the basic unit of a Ladder Diagram. An element consists of two parts as shown in the diagram below.

One is the element symbol which is called "OP Code" and another is the reference number part which is called "Operand".

| Element type                    | Symbol         | Mnemonic instructions                                                               | Remark                              |

|---------------------------------|----------------|-------------------------------------------------------------------------------------|-------------------------------------|

| A Contact (Normally OPEN)       |                | $(ORG \cdot LD \cdot AND \cdot OR) \square \triangle \triangle \triangle \triangle$ | ☐ can be X · Y · M · S ·            |

| B Contact<br>( Normally CLOSE ) |                | (ORG · LD · AND · OR) NOT                                                           | T · C (please refer to section 2.2) |

| Up Differential Contact         | □ΔΔΔΔ<br>— ↑ — | (ORG · LD · AND · OR) TU                                                            |                                     |

| Down Differential Contact       |                | (ORG · LD · AND · OR) TD □△△△△                                                      | □ can be X · Y · M · S              |

| Open Circuit Contact            | <b></b> •      | (ORG · LD · AND · OR) OPEN                                                          |                                     |

| Short Circuit Contact           | •——•           | (ORG · LD · AND · OR) SHORT                                                         |                                     |

| Output Coil                     |                |                                                                                     |                                     |

| Inverse Output Coil             | □ΔΔΔΔ<br>—(/)  |                                                                                     | ☐ can be Y · M · S                  |

| Latching Output Coil            | Y△△△<br>—(L)   | OUT L YAAA                                                                          |                                     |

Remark : please refer to section 2.2 for the ranges of  $X \cdot Y \cdot M \cdot S \cdot T$  and C contacts. Please refer to section 4.2 for the characteristics of  $X \cdot Y \cdot M \cdot S \cdot T$  and C contacts.

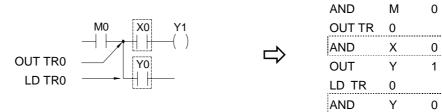

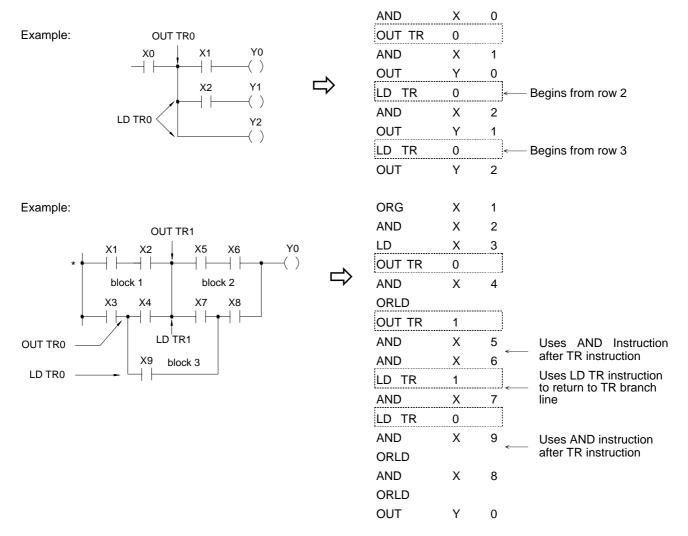

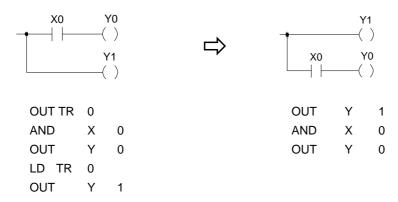

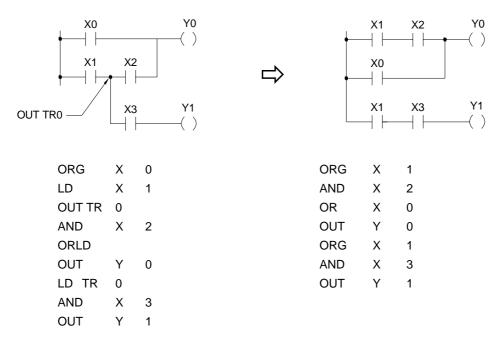

There are three special sequential instructions, namely OUT TRn, LD TRn and FOn, which were not displayed on the Ladder Diagram. Please refer to section 1.6 "Using the Temporary Relay" and section 5.1.4 "Function Output FO".

- ⑤ Node: The connection point between two or more elements (please refer to section 4.3)

- 6 Block: a circuit consists of two or more elements.

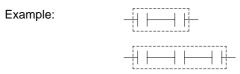

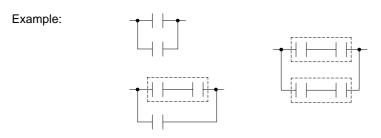

There are two basic types of blocks:

• Serial block: Two or more elements are connected in series to form a single row circuit.

• Parallel block: Parallel block is a type of a parallel closed circuit formed by connecting elements or serial blocks in parallel.

Remark: Complicated block can be formed by the combination of the single element, serial blocks and parallel blocks. When design a Ladder Diagram with mnemonic entry, it is necessary to break down the circuits into element, serial, and parallel blocks. Please refer to section 1.5.

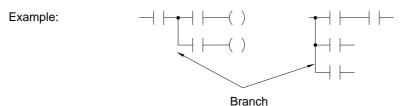

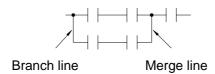

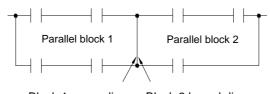

The Branch: In any network, branch is obtained if the right side of a vertical line is connected with two or more rows of circuits.

Merge line is defined as another vertical line at the right side of a branch line that merges the branch circuits into a closed circuit (forming a parallel block). This vertical line is called "Merge line".

If both the right and the left sides of the vertical line are connected with two or more rows of circuits, then it is both a branch line and a merge line as shown in the example below.

#### Example:

Block 1 merge line Block 2 branch line

® Network: Network is a circuit representing a specified function. It consists of the elements, branches, and blocks. Network is the basic unit in the Ladder Diagram which is capable of executing the completed functions, and the program of Ladder Diagram is formed by connecting networks together. The beginning of the network is the origin line. If two circuits are connected by a vertical line, then they belong to the same network. If there is no vertical line between the two circuits, then they belong to two different networks. Figure 1, shows three (1~3) networks.

## 1.4 The Coding Rules of Mnemonic (Users of WinProladder can skip this section)

It's very easy to program FB-PLC with WinProladder software package, just key-in the ladder symbols as they appear on your CRT screen directly to form a ladder diagram program. But for the users who are using FP-08 to program FB-PLC they have to translate ladder diagram into Mnemonic instructions by themselves. Since FP-08 only can input program with Mnemonic instruction, this section till section 1.6 will furnish you with the coding rules to translate ladder diagrams into Mnemonic instructions.

• The program editing directions are from left to right and from top to bottom. Therefore the beginning point of the network must be at the upper left corner of the network. Except the function instruction without the input control, the first instruction of a network must begin with the ORG and only one ORG instruction is permissible per network. Please refer to section 5.1.1 for further explanations.

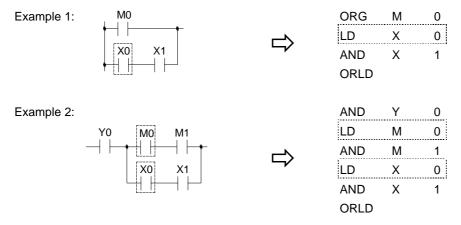

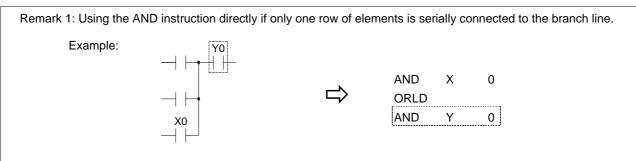

Using LD instruction for connecting vertical lines (origin line or branch line) except at the beginning of the network.

Remark 2: Also using the AND instruction directly if an OUT TR instruction has been used at a branch line to store the node statuses.

• Using AND instruction for serial connection of a single element.

• Using OR instruction for parallel connection of a single element.

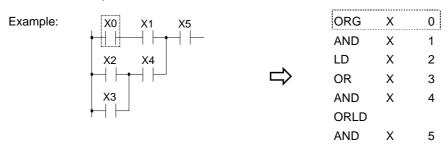

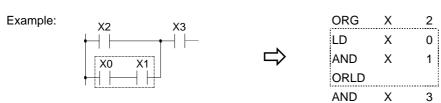

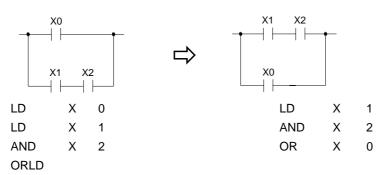

• If the parallel element is a serial block, ORLD instruction must be used.

Remark: If more than two blocks are to be connected in parallel, they should be connected in a top to bottom sequence. For example, block 1 and block 2 should be connected first, then connect block 3 to it and so on. Example: LD Χ 0 0 AND Μ X0 M0 LD Χ 1 AND Μ X1 M1 ORLD X2 M2 2 LD Χ AND Μ 2 ХЗ МЗ ORLD LD 3 Χ AND Μ 3

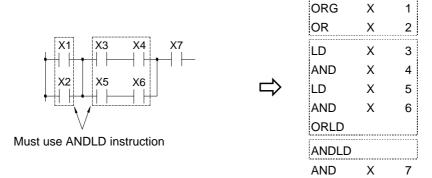

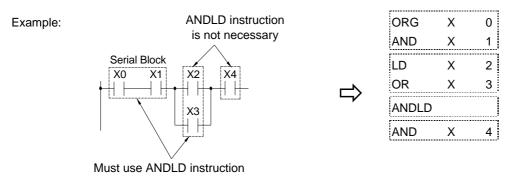

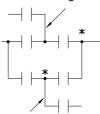

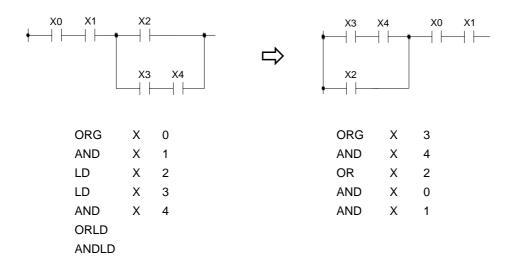

• ANDLD instruction is used to connect parallel blocks in series.

Example:

• The ANDLD instruction must be used if the element or serial block is in front of the parallel block. If the parallel block is in front of the element or serial block, AND instruction can be used to connect all parts together.

• The output coil instruction (OUT) can only be located at end of the network (the right end) and no other elements can be connected to it afterwards. The output coil can not connect to the origin line directly. If you want to connect the output coil to the origin line, connect it serially with a short circuit contact.

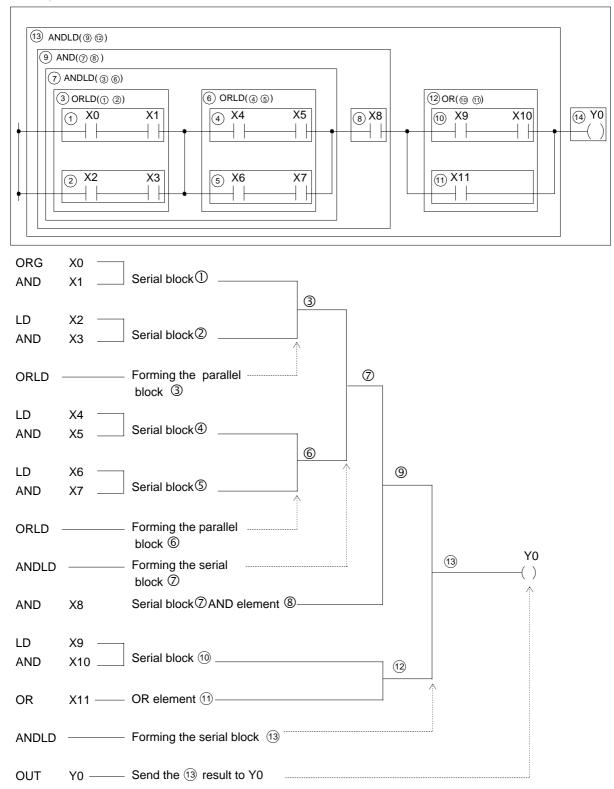

## 1.5 The De-Composition of a Network (Users of WinProladder can skip this section)

The key process of de-composition of a network is to separate the circuits that appear between two vertical lines into independent elements and serial blocks, then coding those elements and serial blocks according to the mnemonic coding rules and then connect them (with ANDLD or ORLD instruction) from left to right and top to bottom to form a parallel or a serial-parallel blocks, and finally to form a complete network.

#### Sample diagram:

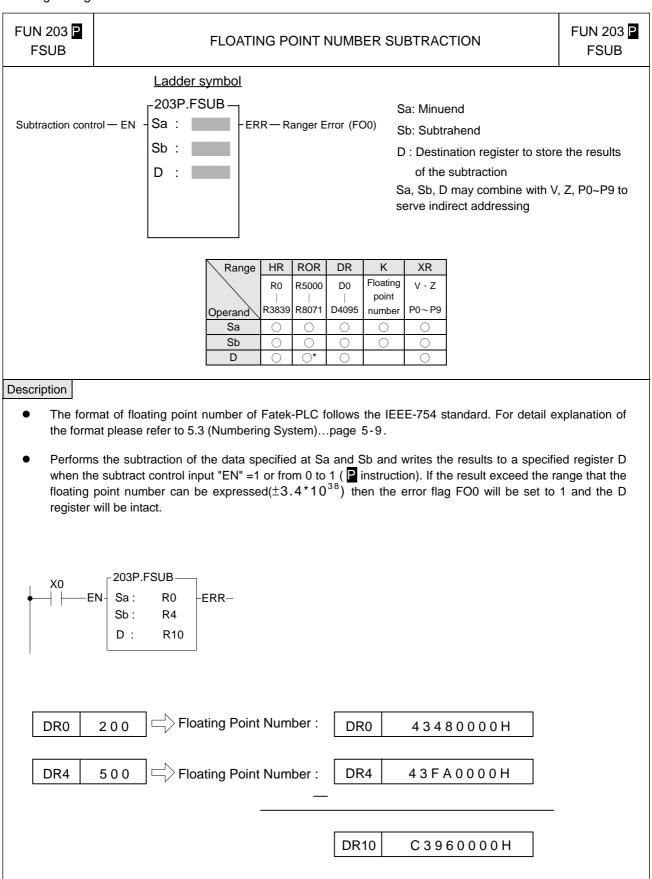

## 1.6

Using Temporary Relays (Users of WinProladder can skip this section)

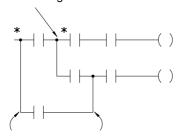

The network de-composition method for mnemonic coding demonstrated in section 1.5 does not apply to the branched circuit or branched block. In order to input the program using the method shown in section 1.5, It must first to store the statuses of branched nodes in temporary relays. The program design should avoid having branched circuit or branched block as much as possible. Please refer the next section "Program Simplification Techniques". Two situations that must use the TR are described at below.

• Branched circuit: Merge line does not exist at the right side of the branch line or there is a merge line at the right side of the branch line but they are not in the same row.

Example:

\* indicates setting of TR relay

Without merge line

Although this branch has merge lines but they are not in the same row, so this is also a branched circuit

• Branched block: The horizontal parallel blocks with a branch in one of the blocks.

Example:

Branch line

Remark 1: The OUT TR instruction must be programmed at the top of the branched point. LD TRn instruction is used at the starting point of the circuits after second rows of the branch line for regaining the branch line status before you can connect any element to the circuits. AND instruction must be used to connect the first element after OUT TRn or LD TRn instruction. LD instruction is not allowed in this case.

Remark 2: A network can have up to 40 TR points and the TR number can not be used repeatedly in the same network. It is recommended to use the numbers 1,2,3... with sequence. The TR number must be the same in the same branch line. For example, if a branch line uses OUT TR0, then starting from row 2, LD TR0 must be used for connection.

Remark 3: If the branch line of a branched circuit or a branched block is the origin line, then ORG or LD instructions can be used directly and TR contact is not necessary.

Remark 4: If any one of the branched circuit rows is not connected to the output coil (there are serially connected elements in between), and other circuits also exist after the second row, a TR instruction must be used at the branch points.

- The above sample diagram shows a typical example of connecting two parallel blocks in series. Block 3 is formed when the element X9 is introduced into the network and the two parallel blocks become the branched blocks.

- TR instruction is not necessary because the (\*) point is the origin line.

- If have already used TR relay to connect two blocks serially, then ANDLD instruction is not necessary.

## 1.7 Program Simplification Techniques

• If a single element is connected in parallel to a serial block, The ORLD instruction can be omitted if the serial block is connected on top of this single element.

• When a single element or a serial block is connected in serial with a parallel block, ANDLD instruction can be omitted if put the parallel block in front.

• If the branch node of a branch circuit is directly connected to the output coil, this coil could be located on top of the branch line (first row) to reduce the code.

• The diagram shown below indicates the TR relay and the ORLD instruction can be omitted.

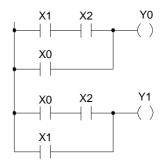

## • Conversion of the bridge circuit

This network structure is not allowed in PLC program

| ORG | Χ | 1 |

|-----|---|---|

| AND | Χ | 2 |

| OR  | Χ | 0 |

| OUT | Υ | 0 |

| ORG | Χ | 0 |

| AND | Χ | 2 |

| OR  | Χ | 1 |

| OUT | Υ | 1 |

## **Chapter 2 FBs-PLC Memory Allocation**

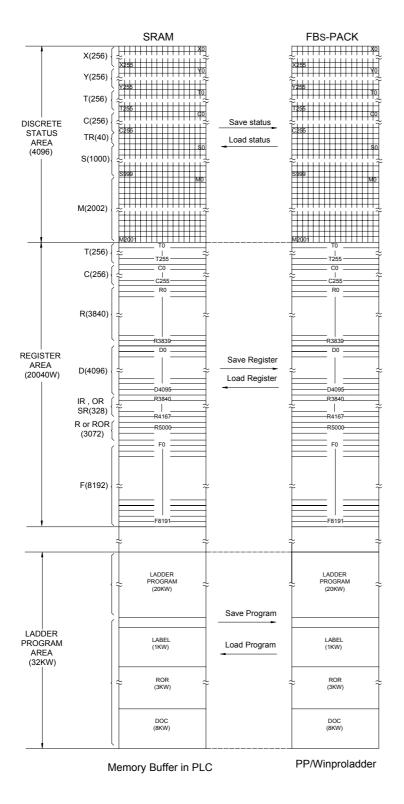

## 2.1 FBs-PLC Memory Allocation

#### Remark:

- 1. When the Read Only Register (ROR) has been configured by the user, the contents of R5000~R8071 (depends on the quantity of configuration) will be loaded from the ROR's during each time of power up or changing from STOP to RUN mode.

The user can access the ROR through the corresponding R5000~R8071.

Write operation of function instructions are prohibited in this

- the corresponding R5000~R8071. Write operation of function instructions are prohibited in this ROR area of corresponding R5000~R8071. The others of R5000~R8071 that have not been configured for ROR, they can work as general purpose registers.

- There is a dedicated area of program memory to store the contents of Read Only Register.

ROR can be configured up to 3072 words in maximum.

## 2.2 Digital and Register Allocations

"\*" is default, user configurable

| Item         |           |                                                |                |                    |                          | Ran                  | ge                                      | Remarks                                                                   |

|--------------|-----------|------------------------------------------------|----------------|--------------------|--------------------------|----------------------|-----------------------------------------|---------------------------------------------------------------------------|

|              | Х         | Input contact ([                               | OI)            |                    |                          | X0~X255 (256         | )                                       | Corresponding to external digital input                                   |

|              | Υ         | Output relay (DO)                              |                |                    |                          | Y0~Y255 (256         | )                                       | Corresponding to external digital output                                  |

|              | TR        | Temporary relay                                |                |                    |                          | TR0~TR39 (40         | ,                                       |                                                                           |

| Dio          |           | Internal                                       |                | Non-retentive      |                          | M0~M799 (800         | ,                                       | Can be configured as retentive type                                       |

| Digital      | М         | Internal<br>relay                              |                | TTOTTTCTCTTTTC     |                          | M1400~M191           |                                         |                                                                           |

|              | IVI       | -                                              |                | Retentiv           | е                        | M800~M1399           | · ,                                     | Can be configured as non-retentive type                                   |

| Bit          |           | Special Relay                                  |                |                    | M1912~M200               | 1 (90)               |                                         |                                                                           |

| 《 Bit Status | S         | Step<br>Relay                                  |                | Non-Retentive      |                          | S0~S499 (500         | )*                                      | S20~S499 can be configured as retentive type                              |

| ~            |           |                                                |                | Retentive          |                          | S500~S999 (5         | (00)*                                   | Can be configured as non-retentive type                                   |

|              | Т         | Timer "Time-l                                  | Jp"            | status c           | ontact                   | T0~T255 (256         | )                                       |                                                                           |

|              | С         | Counter "Counter-Up" status contact            |                |                    | us                       | C0~C255 (256         | 3)                                      |                                                                           |

|              |           |                                                | 0.0            | 1STime             | Base                     | T0~T49 (50)          | <b>k</b>                                |                                                                           |

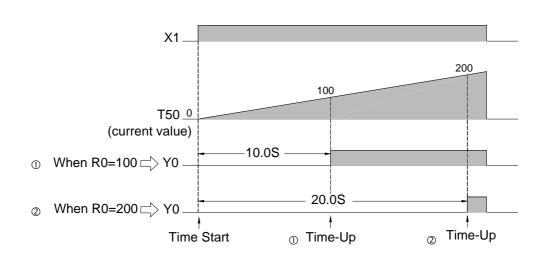

|              | TMR       | Time current value register                    | 0.1            | S Time             | Base                     | $T50\sim T199$ (1    | 50)*                                    | T0~T255 numbers for each time base can be adjusted.                       |

|              |           |                                                | 1S             | Time Ba            | ase                      | $T200\!\sim\!T255$ ( | 56)*                                    | be adjusted.                                                              |

|              |           |                                                | ਨੇ Retentive   |                    | ve                       | C0~C139 (140         | ))*                                     | Can be configured as non-retentive type                                   |

|              |           | Counter current<br>value register              | -bit           | Non-Re             | etentive                 | C140~C199 (60)*      |                                         | Can be configured as retentive type                                       |

|              | CTR       |                                                | 32-bit         | Retenti            | ve                       | C200~C239 (40)*      |                                         | Can be configured as non-retentive type                                   |

|              |           |                                                | bit            | Non-Re             | etentive                 | C240~C255 (1         | 6)*                                     | Can be configured as retentive type                                       |

|              |           | Data Register  Retentive  Retentive  Retentive |                |                    | R0~R2999 (3000)*         |                      | Can be configured as non-retentive type |                                                                           |

|              | HR<br>DR  |                                                |                | Retentive          |                          | D0~D3999 (4000)      |                                         |                                                                           |

|              |           |                                                |                | Non-Retentive      |                          | R3000~R3839          | (840)*                                  | Can be configured as retentive type                                       |

| Register     |           |                                                |                | Retentive          |                          | R5000~R8071          | (3072) *                                | When not configured as ROR, it can serve normal register (for read/write) |

|              | HR<br>ROR |                                                |                | Read Only          |                          | R5000~R8071          | can be set as                           | ROR is stored in special ROR area and                                     |

| ≪ Woı        | KUK       |                                                | Register (ROR) |                    | r (ROR)                  | ROR ~ default :      | setting is (0)*                         | not occupy program space                                                  |

| <u>a</u>     |           |                                                |                | File Register      |                          | F0~F8191 (81         | 92)                                     | Save/retrieved via dedicated instruction                                  |

| Data         | IR        | Input Register                                 |                |                    | R3840~R3903              | 3 (64)               | Corresponding to external numeric input |                                                                           |

| ~            | OR        | Output Register                                |                |                    |                          | R3904~R3967          | (64)                                    | Corresponding to external numeric output                                  |

|              |           | Special system register                        |                |                    | R3968~R416<br>D4000~D409 | , ,                  |                                         |                                                                           |

|              |           | 0.1 mS High-Տլ                                 | pee            | eed Timer Register |                          | R4152~R4154          | (3)                                     |                                                                           |

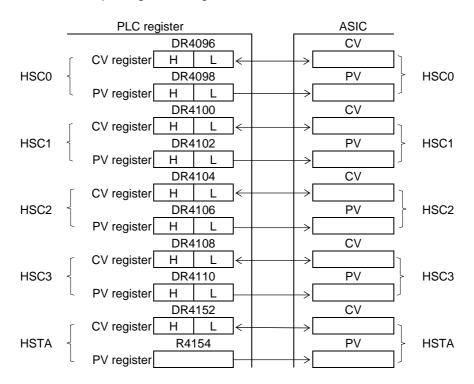

|              |           | HSC                                            | На             | ardware            | (4sets)                  | DR4096~DR4110 (4x4)  |                                         |                                                                           |

|              | SR        | Registers                                      | Sc             | oftware(4          | lsets)                   | DR4112~DR4           | 126 (4x4)                               |                                                                           |

|              |           |                                                | +              | Minute             | Second                   | R4129                | R4128                                   |                                                                           |

|              |           | Calendar                                       |                | Day                | Hour                     | R4131                | R4130                                   |                                                                           |

|              |           | Registers                                      |                | Year               | Month                    | R4133                | R4132                                   |                                                                           |

|              |           | registers                                      |                | , oui              | Week                     | 137100               | R4134                                   |                                                                           |

|              |           |                                                |                |                    | vveek                    |                      | N4134                                   |                                                                           |

|  | FR | File Registers  | F0~F8191(8192)       |  |

|--|----|-----------------|----------------------|--|

|  | XR | Index Registers | V,Z (2) \ P0~P9 (10) |  |

Remark: During power up or changing operation mode from STOP $\rightarrow$ RUN, all contents in non-retentive relays or registers will be cleared to 0; the retentive relays or registers will remain the same state as before.

## 2.3 Special Relay Details

| Relay No.                   | Function                                | Description                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1. Stop, Prohibited Control |                                         |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| M1912                       | Emergency Stop control                  | If 1, PLC will be stopped (but not enter STOP mode) and all outputs OFF.  This bit will be cleared when power up or changing operation mode from STOP→RUN.                                                                                                                                                                                                       |  |  |  |

| M1913                       | Disable external outputs control        | <ul> <li>All external outputs are turn off but the<br/>status of Y0~Y255 inside the PLC will not be affected.</li> </ul>                                                                                                                                                                                                                                         |  |  |  |

| M2001                       | Disable/Enable status retentive control | If M2001 is 0 or enabled, the Disable/Enable status of all contacts will be reset to enable during power up or changing operation mode from STOP→RUN.                                                                                                                                                                                                            |  |  |  |

|                             |                                         | <ul> <li>If M2001 is disabled and force ON, the Disable/Enable status &amp; ON/OFF state of all contacts will remain as before during power up or changing operation mode from STOP→RUN.</li> <li>While testing, it may disable and force ON M2001 to keep the ON/OFF state of disabled contacts, but don't forget to enable the M2001 after testing.</li> </ul> |  |  |  |

| 2. CLEAR Co                 | ontrol                                  |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| M1914                       | Clear Non-Retentive Relays              | Cleared When at 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| M1915                       | Clear Retentive Relays                  | Cleared When at 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| M1916                       | Clear Non-Retentive Registers           | Cleared When at 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| M1917                       | Clear Retentive Registers               | Cleared When at 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| M1918                       | Master Control (MC) Selection           | • If 0, the pulse activated functions within the master control loop will only be executed once at first 0→1 of master control loop.                                                                                                                                                                                                                             |  |  |  |

|                             |                                         | If 1, the pulse activated functions within the master control loop will be executed every time while changing 0→1 of master control loop.                                                                                                                                                                                                                        |  |  |  |

| M1919                       | Function output control                 | •If 0, the functional outputs of some function instructions will memory the output state, even these instructions not been executed.                                                                                                                                                                                                                             |  |  |  |

|                             |                                         | If 1, the functional output of some function instructions without the memory ability.                                                                                                                                                                                                                                                                            |  |  |  |

<sup>%</sup> M1918/M1919 can be set to 0 or 1 at will around the whole program to meet the control requirements.

| Relay No.                                             | Function                                                                                                           | Description                                                                                                                                                                                           |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3. Pulse Sign                                         | nals                                                                                                               |                                                                                                                                                                                                       |

| M1920<br>M1921<br>M1922<br>M1923                      | 0.01S Clock pulse 0.1S Clock pulse 1S Clock pulse 60S Clock pulse                                                  | "RUN" "STOP"  T(M1920)=0.01S  T(M1921)=0.1S  T(M1922)=1S                                                                                                                                              |

| <ul><li>M1924</li><li>✓M1925</li><li>✓M1926</li></ul> | Initial pulse (first scan) ②  Scan clock pulses ③  =0, PLC is working at STOP mode  =1, PLC is working at RUN mode | T(M1923)=60S                                                                                                                                                                                          |

| <b>✓</b> M1927                                        | CTS input status of communication port 1                                                                           | O: CTS True (ON)  1: CTS False (OFF)  When communication port 1 is used to connect with the printer or modem, it can use this signal and a timer to detect whether the printer or the modem is ready. |

| 4. Error Me                                           | ssages                                                                                                             |                                                                                                                                                                                                       |

| M1928<br>M1929<br>M1930                               | Reserved Reserved No expansion unit or exceed the limit on number of I/O points                                    | 1: Indicating no expansion unit or exceed the limit on number of I/O points                                                                                                                           |

| <b>▼</b> M1931                                        | Immediate I/O not in the main unit range                                                                           | 1: Indicating that Immediate I/O not in the main unit range and the main unit cannot RUN                                                                                                              |

| M1932<br>M1933<br>M1934                               | Unused System stack error Reserved                                                                                 | 1: Indicating that system stack error                                                                                                                                                                 |

| M1935                                                 |                                                                                                                    |                                                                                                                                                                                                       |

|                                                       | rt4 Controls (MC/MN)                                                                                               |                                                                                                                                                                                                       |

| M1936                                                 | Port 3 busy indicator                                                                                              | O : Port 3 Busy     1 : Port 3 Ready                                                                                                                                                                  |

| M1937<br>M1938                                        | Port 3 finished indicator Port 4 busy indicator                                                                    | <ul> <li>1 : Port 3 finished all communication transactions</li> <li>0 : Port 4 Busy</li> <li>1 : Port 4 Ready</li> </ul>                                                                             |

| M1939                                                 | Port 4 finished indicator                                                                                          | 1 : Port 4 finished all communication transactions                                                                                                                                                    |

| Relay No.                     | Function                                       | Description                                                                       |

|-------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------|

| 6. HSC0~HSC1 Controls (MC/MN) |                                                |                                                                                   |

| M1940                         | HSC0 software Mask                             | • 1: Mask                                                                         |

| M1941                         | HSC0 software Clear                            | • 1: Clear                                                                        |

| M1942                         | HSC0 software Direction                        | O: Count-up, 1: Count-down                                                        |

| M1943                         | Reserved                                       |                                                                                   |

| M1944                         | Reserved                                       |                                                                                   |

| M1945                         | Reserved                                       |                                                                                   |

| M1946                         | HSC1 software Mask                             | • 1: Mask                                                                         |

| M1947                         | HSC1software Clear                             | • 1: Clear                                                                        |

| M1948                         | HSC1 software Direction                        | O: Count-up, 1: Count-down                                                        |

| M1949                         | Reserved                                       |                                                                                   |

| M1950                         | Port 3 communication indicator                 | 1: Port 3 has received and transmitted a message                                  |

| M1951                         | Port 4 communication indicator                 | 1: Port 4 has received and transmitted a message                                  |

| 7. RTC Con                    | trols                                          |                                                                                   |

| M1952                         | RTC setting                                    |                                                                                   |

| M1953                         | ±30 second Adjustment                          |                                                                                   |

| <b>▼</b> M1954                | RTC installation checking                      |                                                                                   |

| <b>▼</b> M1955                | Set value error                                |                                                                                   |

| 8. Communio                   | cation/Timing/Counting Controls                |                                                                                   |

| M1956                         | Selection of Message Frame Interval            | • 0 : Use system default value as Message Frame Interval                          |

|                               | Detection Time                                 | Detection Time for Modbus RTU communication protocol                              |

|                               |                                                | • 1 : Use the high byte value of R4148 as Message Frame Interval                  |

|                               |                                                | Detection Time for Modbus RTU protocol                                            |

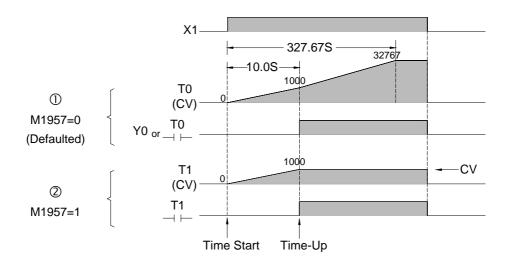

| M1957                         | The CV value control after the timer "Time Up" | 0: The CV value will continue timing until the upper limit is met after "Time Up" |

|                               |                                                | • 1: The CV value will stop at the PV value after "Time Up" (User                 |

|                               |                                                | may control M1957 within the program to control the individual                    |

|                               |                                                | timer )                                                                           |

| M1958                         | Communication port 2 High Speed                | 0: Set Port 2 to Normal Speed Link                                                |

|                               | Link mode selection                            | 1: Set Port 2 to High Speed CPU Link                                              |

|                               |                                                |                                                                                   |

| M1959                         | Modem dialing signal selection                 | 0: Dialing by TONE when Port 1 connecting with Modem.                             |

|                               |                                                | 1: Dialing by PULSE when Port 1 connecting wit     Modem.                         |

| M1960                         | Port 1 busy indicator                          | • 0 : Port 1 Busy                                                                 |

|                               |                                                | • 1 : Port 1 Ready                                                                |

| M1961                         | Port 1 finished indicator                      | 1 : Port 1 finished all communication transactions                                |

| M1962                         | Port 2 busy indicator                          | • 0 : Port 2 Busy                                                                 |

|                               |                                                | • 1 : Port 2 Ready                                                                |

| M1963                         | Port 2 finished indicator                      | 1 : Port 2 finished all communication transactions                                |

| M1964                         | Modem dialing control                          | If Port 1 is connected with Modem,                                                |

|                               |                                                | when signal 0→1 will dial the phone number;                                       |

|                               |                                                | when signal 1→0 will hang-up the phone.                                           |

|                               |                                                |                                                                                   |

|                               |                                                |                                                                                   |

| Relay No.  | Function                                       | Description                                                                                                                                                 |

|------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M1965      | Dialing success flag                           | • 1: Indicating that dialing is successful (when Port 1 is connected with Modem).                                                                           |

| M1966      | Dialing fail flag                              | 1: Indicating that dialing has failed (when Port 1 is connected with Modem).                                                                                |

| M1967      | Port 2 High Speed Link working                 | 0: Continuous cycle.                                                                                                                                        |

|            | mode selection                                 | 1: One cycle only. It will stop when the last communication transaction is completed (only effective at the master station).                                |

| M1968      | Step program status                            | • 1: Indicating that there are more than 16 active steps in the step program at the same time.                                                              |

| M1969      | Indirect addressing illegal write flag         | 1: Indicating that a function with index addressing attempts to write cross over the boundary of different type of data.                                    |

| M1970      | Port 0 status                                  | 1: Port 0 has received and transmitted a message                                                                                                            |

| M1971      | Port 1 status                                  | 1: Port1 has received and transmitted a message                                                                                                             |

| M1972      | Port 2 status                                  | 1: Port2 has received and transmitted a message                                                                                                             |

| M1973      | The CV value control after counting "Count-Up" | O: Indicating that the CV value will continue counting up to the upper limit after "Time-Up".                                                               |

|            |                                                | 1: Indicating that the CV value will stop at the PV value after<br>"Count-Up" (User may control M1973 within the program to control the individual counter) |

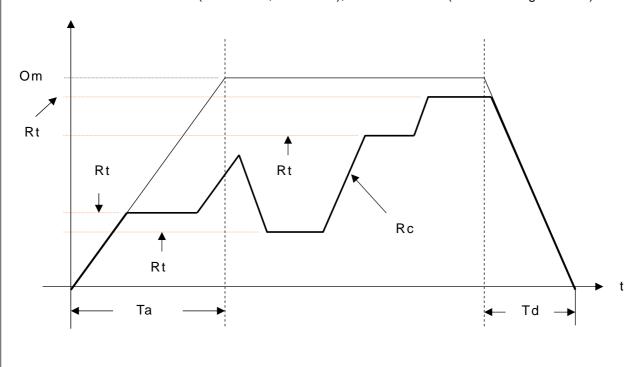

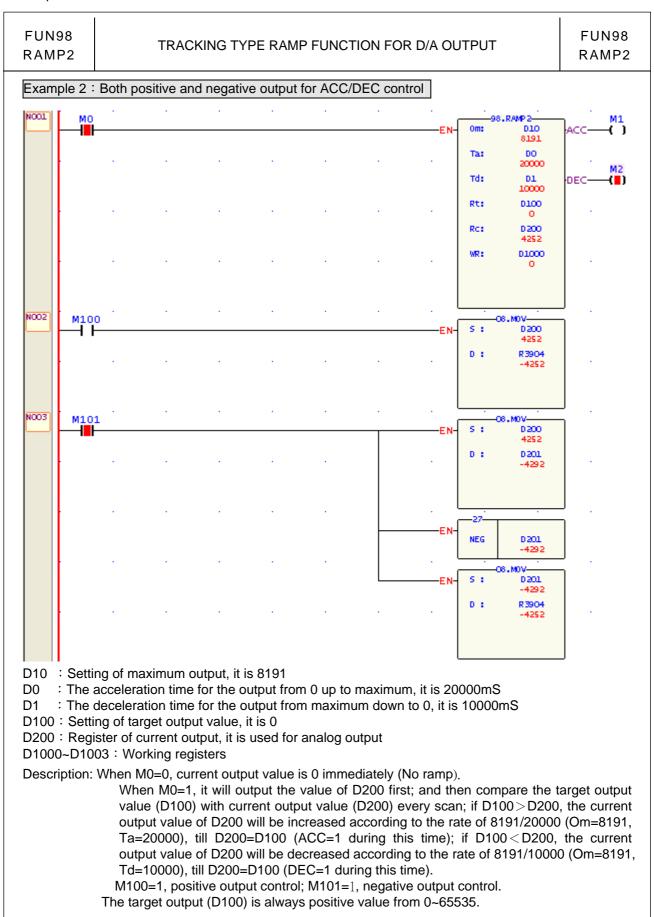

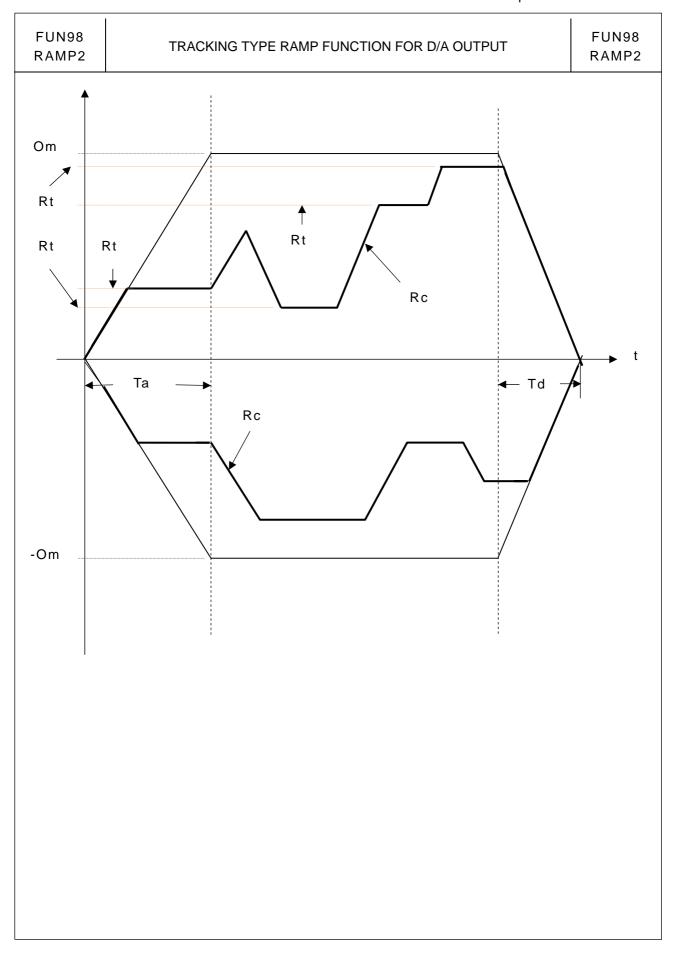

| M1974      | RAMP function slope control                    | 0: Time control for ramping                                                                                                                                 |

|            |                                                | 1: Equivalent slope control for ramping                                                                                                                     |

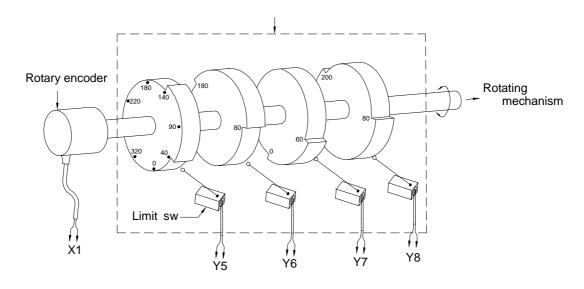

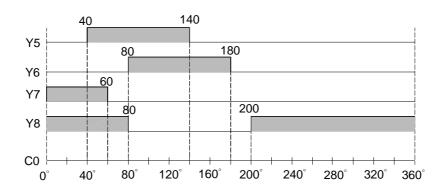

| M1975      | CAM function (FUN112) selection                | • 1: For the circular applications where the electric CAM switch (FUN112) can support the wrap around situation like the angle from 359° cross to 0°        |

| 9. HSC2~HS | C7 Controls                                    |                                                                                                                                                             |

| M1976      | HSC2 software Mask                             | • 1: Mask                                                                                                                                                   |

| M1977      | HSC2 software Clear                            | • 1: Clear                                                                                                                                                  |

| M1978      | HSC2 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1979      | HSC3 software Mask                             | • 1: Mask                                                                                                                                                   |

| M1980      | HSC3 software Clear                            | • 1: Clear                                                                                                                                                  |

| M1981      | HSC3 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1982      | HSC4 software Mask                             | • 1: Mask                                                                                                                                                   |

| M1983      | HSC4 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1984      | HSC5 software MASK                             | • 1: Mask                                                                                                                                                   |

| M1985      | HSC5 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1986      | HSC6 software Mask                             | • 1: Mask                                                                                                                                                   |

| M1987      | HSC6 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1988      | HSC7 software Mask                             | • 1: Mask                                                                                                                                                   |

| M1989      | HSC7 software Direction                        | 0: Count-up, 1: Count-down                                                                                                                                  |

| M1990      | Reserved                                       |                                                                                                                                                             |

| Relay No.  | Function                               | Description                                      |

|------------|----------------------------------------|--------------------------------------------------|

| 10. PSO0∼P | OS3 Controls                           |                                                  |

| M1991      | Selection of stopping the pulse output | 0 : Immediately stop while stopping pulse output |

|            | (FUN140)                               | 1 : Slow down stop while stopping pulse output   |

| M1992      | PSO0 Busy indicator                    | • 0 : PSO0 Busy                                  |

|            |                                        | • 1 : PSO0 Ready                                 |

| M1993      | PSO1 Busy indicator                    | • 0 : PSO1 Busy                                  |

|            |                                        | • 1 : PSO1 Ready                                 |

|            |                                        |                                                  |

| M1994      | PSO2 Busy indicator                    | • 0 : PSO2 Busy                                  |

|            |                                        | • 1 : PSO2 Ready                                 |

| M1995      | PSO3 Busy indicator                    | • 0 : PSO3 Busy                                  |

|            |                                        | • 1 : PSO3 Ready                                 |

| M1996      | PSO0 Finished indicator                | 1 : PSO0 finished the last step of motion        |

| M1997      | PSO1 Finished indicator                | • 1 : PSO1 finished the last step of motion      |

| M1998      | PSO2 Finished indicator                | 1 : PSO2 finished the last step of motion        |

| M1999      | PSO3 Finished indicator                | • 1 : PSO3 finished the last step of motion      |

| M2000      | Selection of Multi-Axis                | • 1: Synchronized Multi-Axis                     |

|            | synchronization for High Speed Pulse   |                                                  |

|            | Output (FUN140)                        |                                                  |

## 2.4 Special Registers Details

| Register No.               | Function                                                       | Description                   |

|----------------------------|----------------------------------------------------------------|-------------------------------|

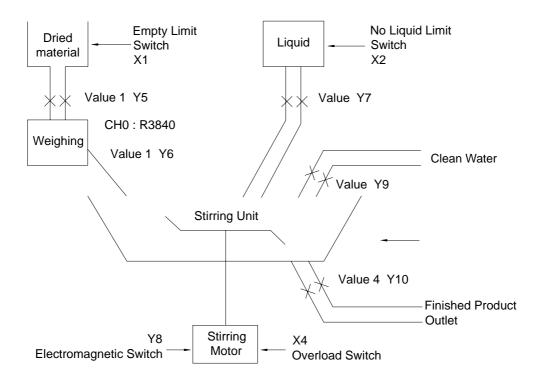

| R3840<br> <br>R3903        | Input Registers CH0: R3840                                     | For Analog or Numeric inputs  |

| R3904                      | CH63: R3903 Output Registers CH0: R3904                        | For Analog or Numeric outputs |

| R3967                      | <br>CH63 : R3967                                               |                               |

| R3968<br> <br>R3980        | Define stimulate Modbus equipment                              |                               |

| R3981<br> <br> <br>  R3999 | Reserved                                                       |                               |

| R4000                      | Reserved                                                       |                               |

| R4001                      | Reserved                                                       |                               |

| R4002                      | Reserved                                                       |                               |

| R4003<br> <br>R4004        | Define FUN86 temperature reading value at starting/end address |                               |

| value = |

|---------|

| value – |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

| Register No.        | Function                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

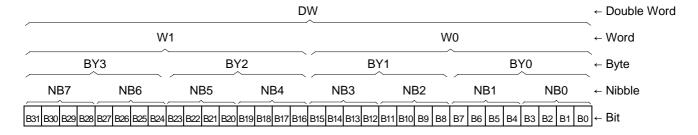

| R4026               | Total Expansion Output Registers                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                     |